# Op Amp Applications Handbook

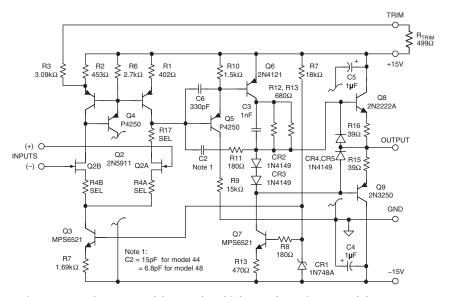

Analog Devices, Inc.

By Walt Jung

# **Op Amp Applications Handbook**

Walt Jung, Editor with the technical staff of Analog Devices

A Volume in the Analog Devices Series

Newnes is an imprint of Elsevier 30 Corporate Drive, Suite 400, Burlington, MA 01803, USA Linacre House, Jordan Hill, Oxford OX2 8DP, UK

Copyright © 2005 by Analog Devices, Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone: (+44) 1865 843830, fax: (+44) 1865 853333, e-mail: permissions@elsevier.com.uk. You may also complete your request on-line via the Elsevier homepage (http://elsevier.com), by selecting "Customer Support" and then "Obtaining Permissions."

Recognizing the importance of preserving what has been written, Elsevier prints its books on acid-free paper whenever possible.

#### **Library of Congress Cataloging-in-Publication Data**

Jung, Water G.

Op Amp applications handbook / by Walt Jung.

p. cm – (Analog Devices series)

ISBN 0-7506-7844-5

1. Operational amplifiers—Handbooks, manuals, etc. I. Title. II. Series.

TK7871.58.O618515 2004 621.39'5--dc22

2004053842

#### British Library Cataloguing-in-Publication Data

A catalogue record for this book is available from the British Library.

For information on all Newnes publications visit our Web site at www.books.elsevier.com

04 05 06 07 08 09 10 9 8 7 6 5 4 3 2 1

Printed in the United States of America

# **Contents**

| Foreword                                                   | <i>vii</i> |

|------------------------------------------------------------|------------|

| Preface                                                    | ix         |

| Acknowledgments                                            |            |

| Op Amp History Highlights                                  | <i>xv</i>  |

| Chapter 1: Op Amp Basics                                   | 3          |

| Section 1-1: Introduction                                  | 5          |

| Section 1-2: Op Amp Topologies                             | 23         |

| Section 1-3: Op Amp Structures                             | 31         |

| Section 1-4: Op Amp Specifications                         | 51         |

| Section 1-5: Precision Op Amps                             | 89         |

| Section 1-6: High Speed Op Amps                            | 97         |

| Chapter 2: Specialty Amplifiers                            | 121        |

| Section 2-1: Instrumentation Amplifiers                    | 123        |

| Section 2-2: Programmable Gain Amplifiers                  | 151        |

| Section 2-3: Isolation Amplifiers                          | 161        |

| Chapter 3: Using Op Amps with Data Converters              | 173        |

| Section 3-1: Introduction                                  | 173        |

| Section 3-2: ADC/DAC Specifications                        | 179        |

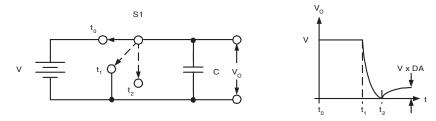

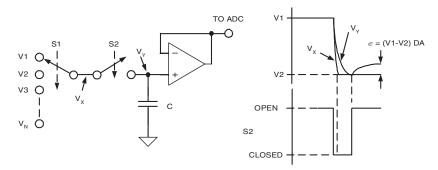

| Section 3-3: Driving ADC Inputs                            | 193        |

| Section 3-4: Driving ADC/DAC Reference Inputs              | 213        |

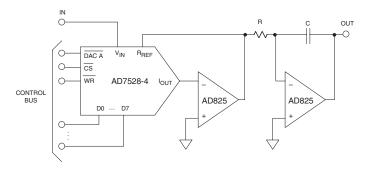

| Section 3-5: Buffering DAC Outputs                         | 217        |

| Chapter 4: Sensor Signal Conditioning                      | 227        |

| Section 4-1: Introduction                                  | 227        |

| Section 4-2: Bridge Circuits                               | 231        |

| Section 4-3: Strain, Force, Pressure and Flow Measurements | 247        |

| Section 4-4: High Impedance Sensors                        | 257        |

| Section 4-5: Temperature Sensors                           | 285        |

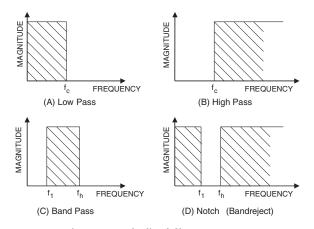

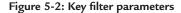

| Chapter 5: Analog Filters                                  | 309        |

| Section 5-1: Introduction                                  | 309        |

|                                                            |            |

#### Contents

|    | Section 5-3: Time Domain Response                           | . 323 |

|----|-------------------------------------------------------------|-------|

|    | Section 5-4: Standard Responses                             | . 325 |

|    | Section 5-5: Frequency Transformations                      | . 349 |

|    | Section 5-6: Filter Realizations                            | .357  |

|    | Section 5-7: Practical Problems in Filter Implementation    | . 393 |

|    | Section 5-8: Design Examples                                | . 403 |

| Ch | napter 6: Signal Amplifiers                                 | 423   |

|    | Section 6-1: Audio Amplifiers                               | . 423 |

|    | Section 6-2: Buffer Amplifiers and Driving Capacitive Loads | . 493 |

|    | Section 6-3: Video Amplifiers                               | . 505 |

|    | Section 6-4: Communication Amplifiers                       | . 545 |

|    | Section 6-5: Amplifier Ideas.                               | . 567 |

|    | Section 6-6: Composite Amplifiers                           | . 587 |

| Ch | napter 7: Hardware and Housekeeping Techniques              | 607   |

|    | Section 7-1: Passive Components                             | . 609 |

|    | Section 7-2: PCB Design Issues                              | . 629 |

|    | Section 7-3: Op Amp Power Supply Systems                    | . 653 |

|    | Section 7-4: Op Amp Protection                              | . 675 |

|    | Section 7-5: Thermal Considerations                         | . 699 |

|    | Section 7-6: EMI/RFI Considerations                         | . 707 |

|    | Section 7-7: Simulation, Breadboarding and Prototyping      | . 737 |

| Ch | napter 8: Op Amp History                                    | 765   |

|    | Section 8-1: Introduction                                   | . 767 |

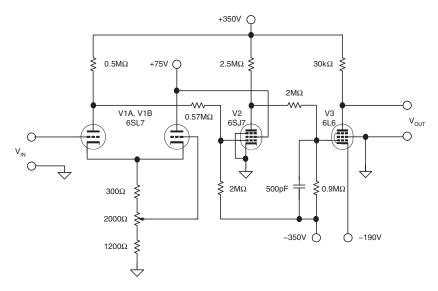

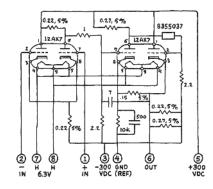

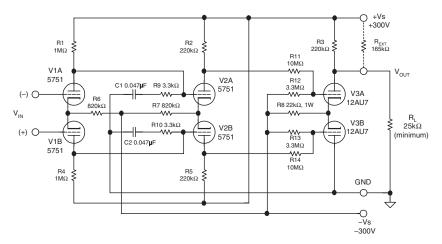

|    | Section 8-2: Vacuum Tube Op Amps                            | . 773 |

|    | Section 8-3: Solid-State Modularand Hybrid Op Amps          | . 791 |

|    | Section 8-4: IC Op Amps                                     | . 805 |

| l  | day.                                                        | 021   |

### **Foreword**

The signal-processing products of Analog Devices, Inc. (ADI), along with those of its worthy competitors, have always had broad applications, but in a special way: they tend to be used in critical roles making possible—and at the same time limiting—the excellence in performance of the device, instrument, apparatus, or system using them.

Think about the *op amp*—how it can play a salient role in amplifying an ultrasound wave from deep within a human body, or measure and help reduce the error of a feedback system; the *data converter*—and its critical position in translating rapidly and accurately between the world of tangible physics and the world of abstract digits; the *digital signal processor*—manipulating the transformed digital data to extract information, provide answers, and make crucial instant-by-instant decisions in control systems; *transducers*, such as the life-saving MEMS accelerometers and gyroscopes; and even *control chips*, such as the one that empowers the humble thermometric junction placed deep in the heart of a high-performance—but very vulnerable—microcomputer chip.

From its founding two human generations ago, in 1965, ADI has been committed to a leadership role in designing and manufacturing products that meet the needs of the existing market, anticipate the near-term needs of present and future users, and envision the needs of users yet unknown—and perhaps *unborn*—who will create the markets of the future. These existing, anticipated and envisioned "needs" must perforce include far more than just the design, manufacture and timely delivery of a physical device that performs a function reliably to a set of specifications at a competitive price.

We've always called a product that satisfies these needs "the augmented product," but what does this mean?

The *physical* product is a highly technological product that, above all, requires *knowledge* of its possibilities, limitations and subtleties. But when the earliest generations—and to some extent later generations—of such a product appear in the marketplace, there exist few (if any) school courses that have produced graduates proficient in its use. There are few knowledgeable designers who can foresee its possibilities. So we have the huge task of creating awareness; teaching about principles, performance measures, and existing applications; and providing ideas to stimulate the imagination of those creative users who will provide our next round of challenges.

This problem is met by deploying people and publications. The *people* are Applications Engineers, who can deal with user questions arriving via phone, fax, and e-mail—as well as working with users in the field to solve particular problems. These experts also spread the word by giving seminars to small and large groups for purposes from inspiring the creative user to imbuing the system, design, and components engineer with the nuts-and-bolts of practice. The *publications*—both in hard copy and on-line—range from authoritative handbooks, such as the present volume, comprehensive data sheets, application notes, hardware and software manuals, to periodic publications, such as "Solutions Bulletins" and our unique *Analog Dialogue*—the sole survivor among its early peers—currently in its 38th year of continuous publication in print and its 6th year of regular publication on the Internet.

This book is the ultimate expression of product "augmentation" as it relates to operational amplifiers. In some senses, it can be considered a descendant of two early publications. The first is a 1965 set of *Op Amp*

#### Foreword

*Notes* (Parts 1, 2, 3, and 4), written by Analog Devices co-founder Ray Stata, with the current text directly reflecting these roots. Much less directly would be the 1974 first edition of the *IC Op Amp Cookbook*, by Walter Jung. Although useful earlier books had been published by Burr-Brown, and by Dan Sheingold at Philbrick, these two timely publications were seminal in the early days of the silicon era, advocating the understanding and use of IC op amps to a market in the process of growing explosively. Finally, and perhaps more important to current students of the op amp art, would be the countless contributions of ADI design and applications engineers, amassed over the years and so highly evident within this new book.

Operational amplifiers have been marketed since 1953, and practical IC op amps have been available since the late 1960s. Yet, half a century later, there is still a need for a book that embraces the many aspects of op amp technology—one that is thorough in its technical content, that looks forward to tomorrow's uses and back to the principles and applications that still make op amps a practical necessity today. We believe that this is such a book, and we commend Walter Jung for "augmenting" the op amp in such an interesting and accessible form.

Ray Stata

Daniel Sheingold

Norwood, Massachusetts, April 28, 2004

# Preface

**Op Amp Applications Handbook** is another book on the operational amplifier, or *op amp*. As the name implies, it covers the application of op amps, but does so on a broader scope. Thus it would be incorrect to assume that this book is simply a large collection of app notes on various devices, as it is far more than that. Any IC manufacturer in existence since the 1960s has ample application data on which to draw. In this case, however, Analog Devices, Inc. has had the benefit of applications material with a history that goes back beyond early IC developments to the preceding period of solid-state amplifiers in modular form, with links to the even earlier era of vacuum tube op amps and analog computers, where the operational amplifier began.

This book brings some new perspectives to op amp applications. It adds insight into op amp origins and historical developments not available elsewhere. Within its major chapters it also offers fundamental discussions of basic op amp operation; the roles of various device types (including both op amps and other specialty amplifiers, such as instrumentation amplifiers); the procedures for optimal interfacing to other system components such as ADCs and DACs, signal conditioning and filtering in data processing systems, and a wide variety of signal amplifiers. The book concludes with practical discussions of various hardware issues, such as passive component selection, printed circuit design, modeling and breadboarding, etc. In short, while this book does indeed cover op amp applications, it also covers a host of closely related design topics, making it a formidable toolkit for the analog designer.

The book is divided into 8 major chapters, and occupies nearly 1000 pages, including index. The chapters are outlined as follows:

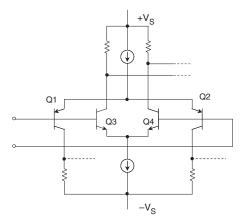

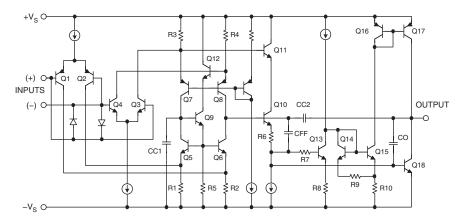

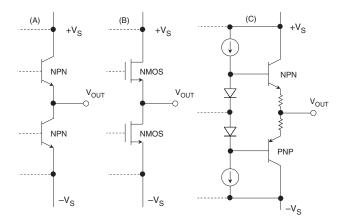

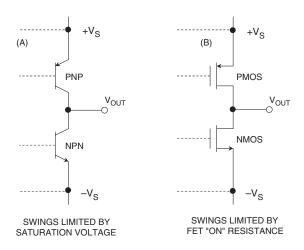

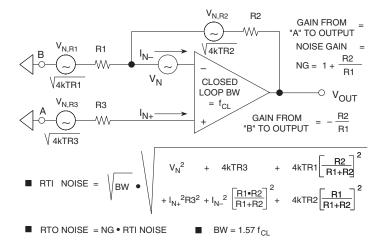

Chapter 1, *Op Amp Basics*, has five sections authored by James Bryant, Walt Jung, and Walt Kester. This chapter provides fundamental op amp operating information. An introductory section addresses their ideal and non-ideal characteristics along with basic feedback theory. It then spans op amp device topologies, including voltage and current feedback models, op amp internal structures such as input and/or output architectures, the use of bipolar and/or FET devices, single supply/dual supply considerations, and op amp device specifications that apply to all types. The two final sections of this chapter deal with the operating characteristics of precision and high-speed op amp types. This chapter, itself a book-within-a-book, occupies about 118 pages.

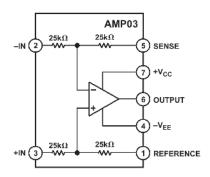

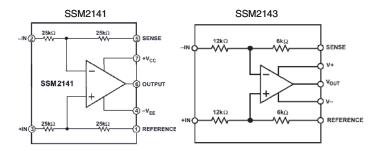

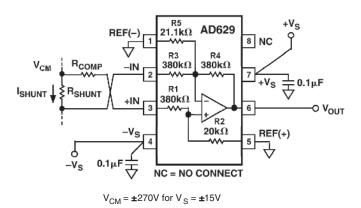

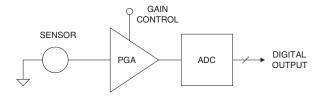

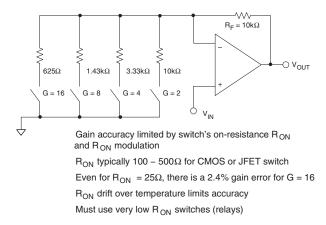

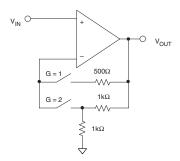

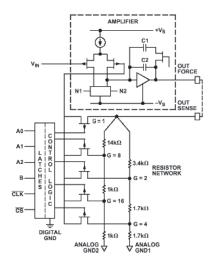

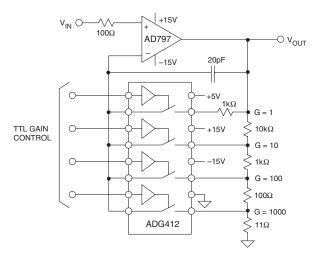

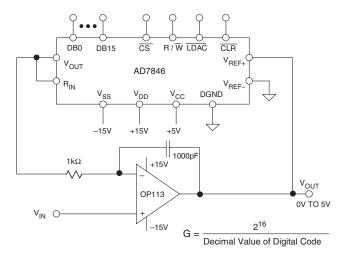

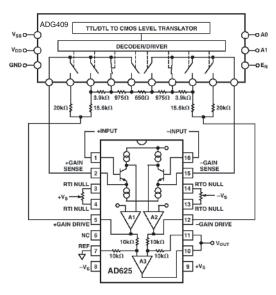

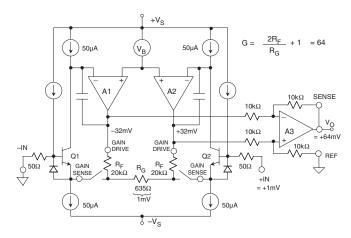

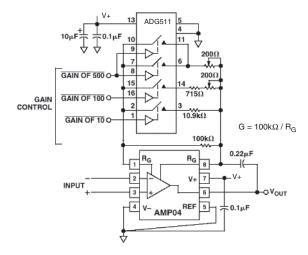

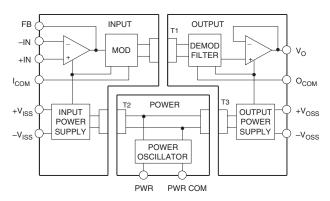

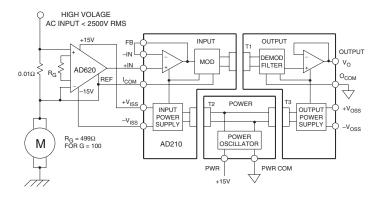

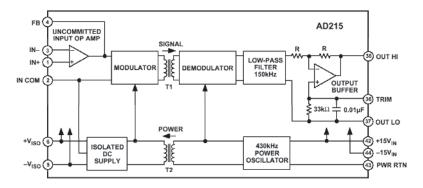

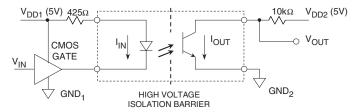

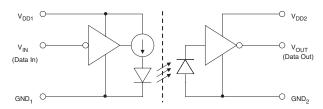

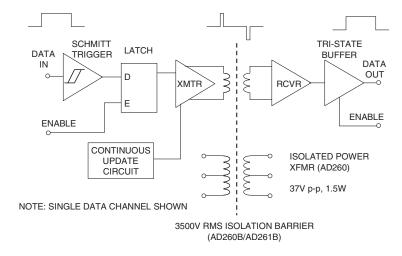

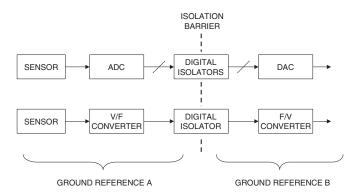

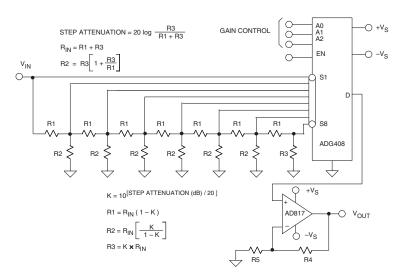

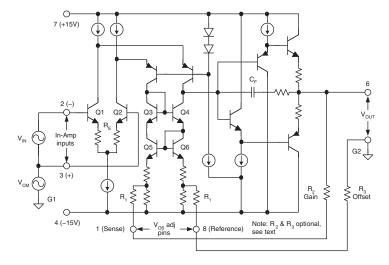

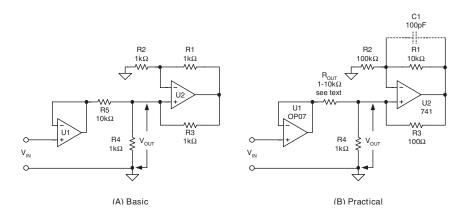

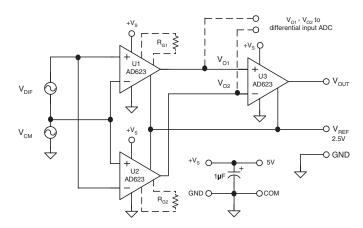

Chapter 2, *Specialty Amplifiers*, has three sections authored by Walt Kester, Walt Jung, and James Bryant. This chapter provides information on those commonly used amplifier types that use op amp-like principles, but aren't op amps themselves—instead they are specialty amplifiers. The first section covers the design and application of differential input, single-ended output amplifiers, known as instrumentation amplifiers. The second section is on programmable gain amplifiers, which are op amp or instrumentation amplifier stages, designed to be dynamically addressable for gain. The final section of the chapter is on isolation amplifiers, which provide galvanic isolation between sections of a system. This chapter occupies about 52 pages.

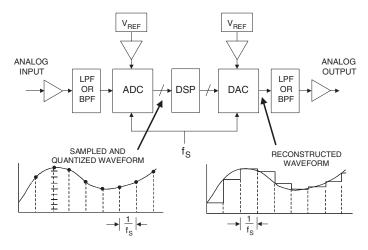

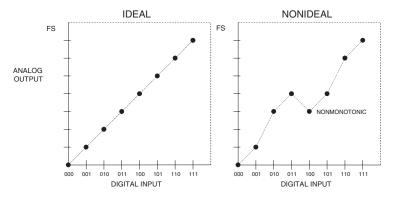

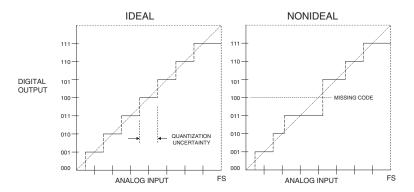

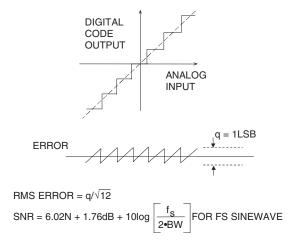

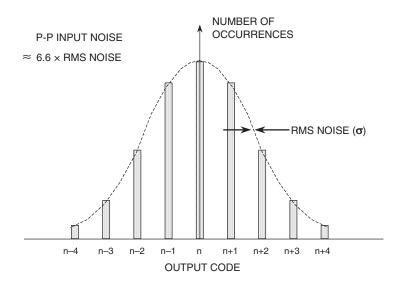

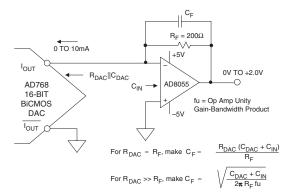

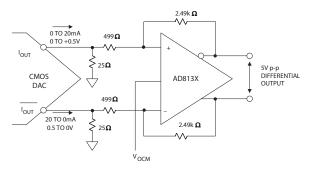

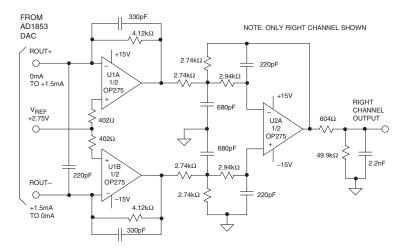

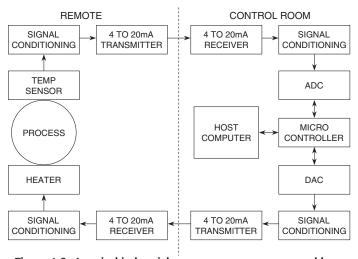

Chapter 3, *Using Op Amps with Data Converters*, has five sections authored by Walt Kester, James Bryant, and Paul Hendriks. The first section is an introductory one, introducing converter terms and the concept of minimizing conversion degradation within the design of an op amp interface. The second section covers ADC and DAC specifications, including such critically important concepts as linearity, monotonicity,

missing codes. The third section covers driving ADC inputs in both single-ended and differential signal modes, op amp stability and settling time issues, level shifting, etc. This section also includes a discussion of dedicated differential driver amplifier ICs, as well as op amp-based ADC drivers. The fourth section is concerned with driving converter reference inputs, and optimal use of sources. The fifth and final section covers DAC output buffer amplifiers, using both standard op amp circuits as well as differential driver ICs. This chapter occupies about 54 pages.

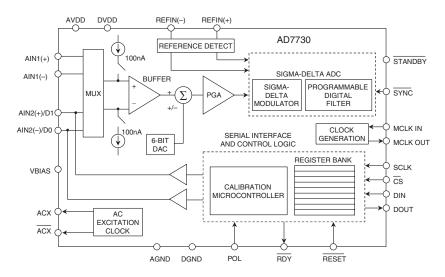

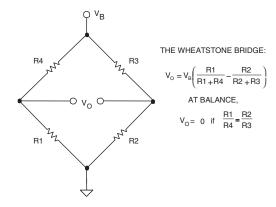

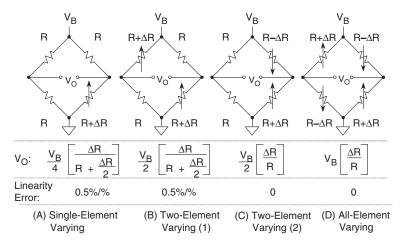

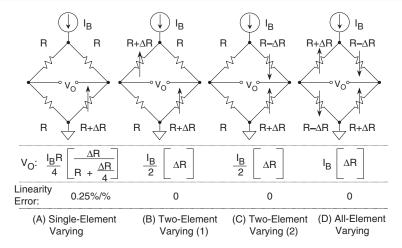

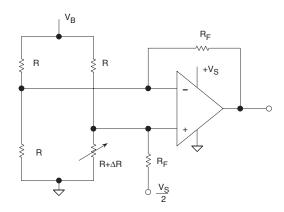

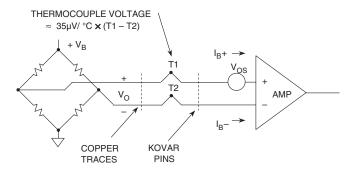

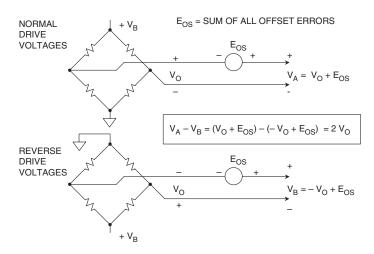

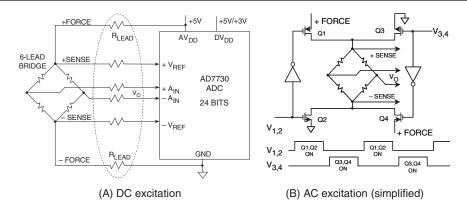

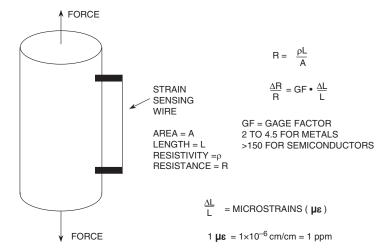

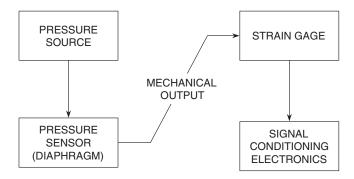

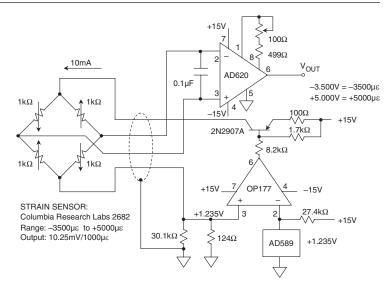

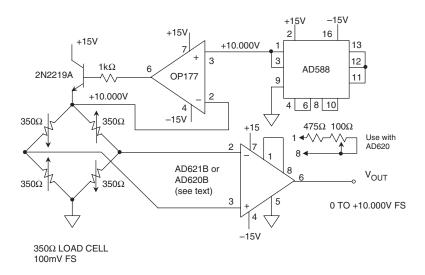

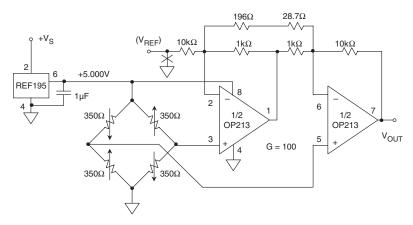

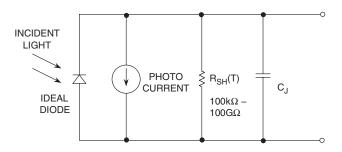

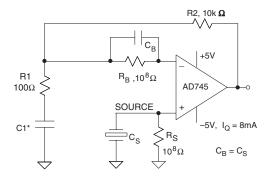

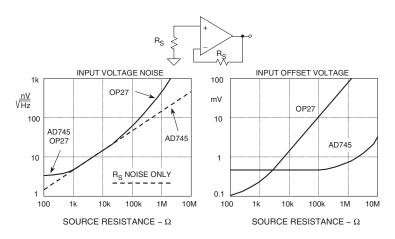

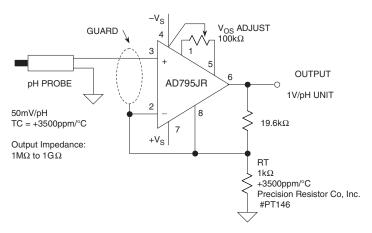

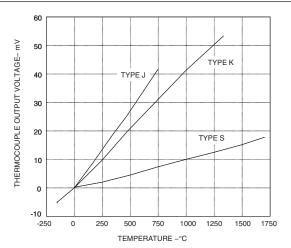

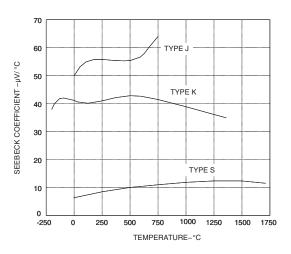

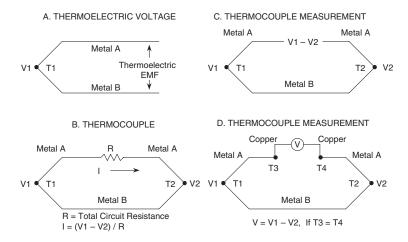

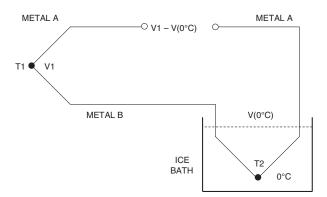

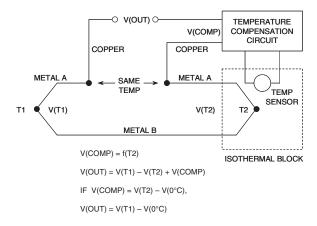

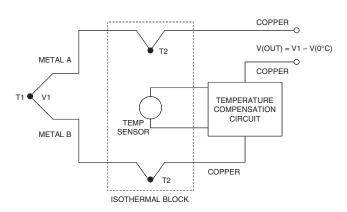

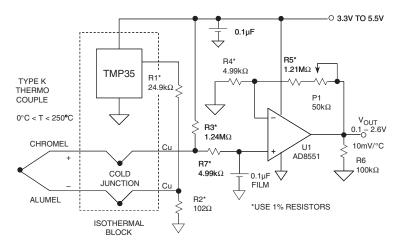

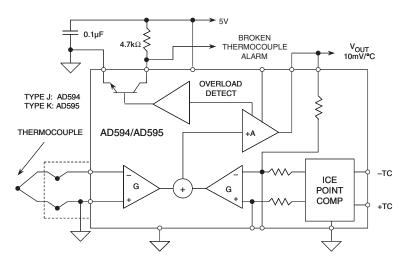

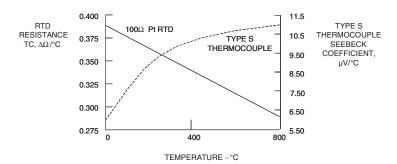

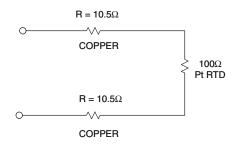

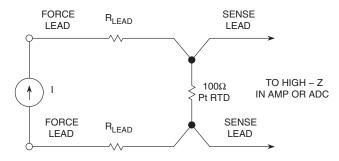

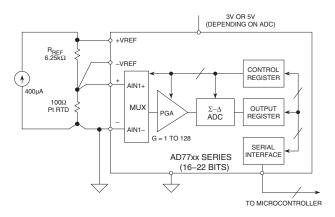

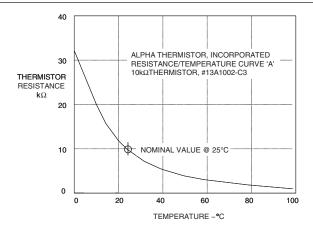

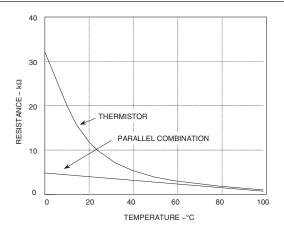

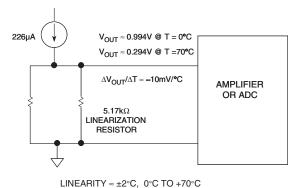

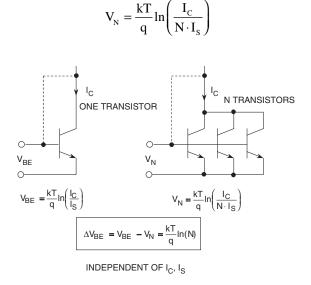

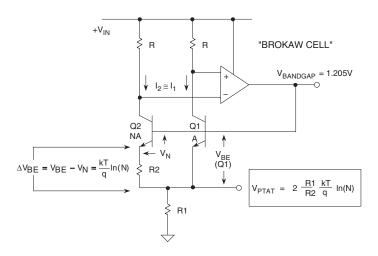

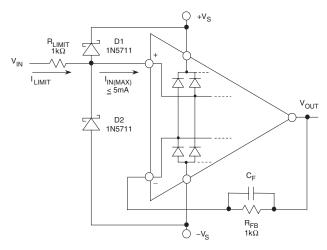

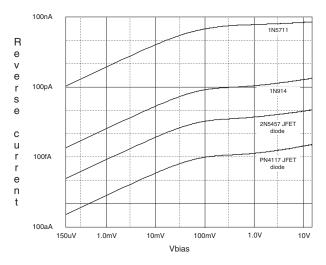

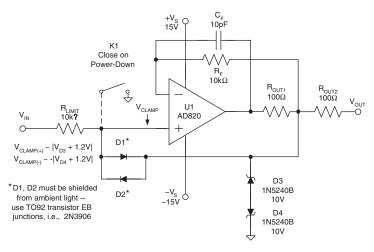

Chapter 4, *Sensor Signal Conditioning*, has five sections authored by Walt Kester, James Bryant, Walt Jung, Scott Wurcer, and Chuck Kitchin. After an introductory section on sensor types and their processing requirements, the remaining four sections deal with the different sensor types. The second section is on bridge circuits, covering the considerations in optimizing performance with respect to bridge drive mode, output mode, and impedance. The third section covers strain, force, pressure, and flow measurements, along with examples of high performance circuits with representative transducers. The fourth section, on high impedance sensors, covers a multitude of measurement types. Among these are photodiode amplifiers, charge amplifiers, and pH amplifiers. The fifth section of the chapter covers temperature sensors of various types, such as thermocouples, RTDs, thermistor and semiconductor-based transducers. This chapter occupies about 82 pages.

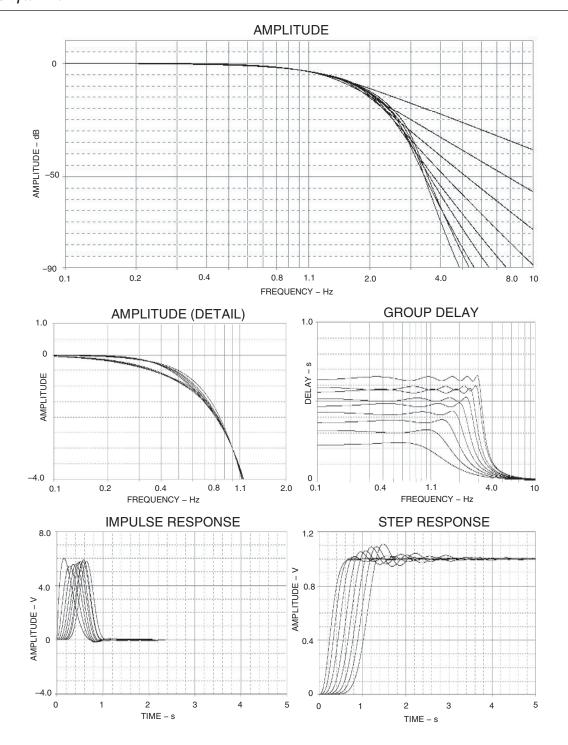

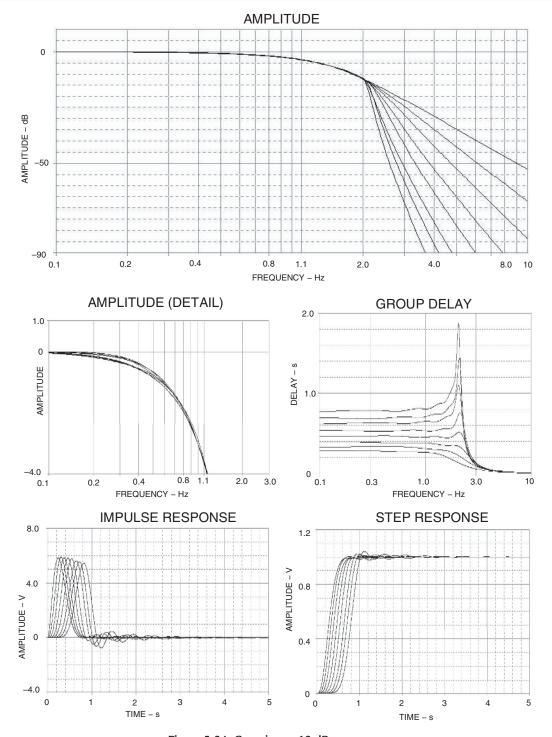

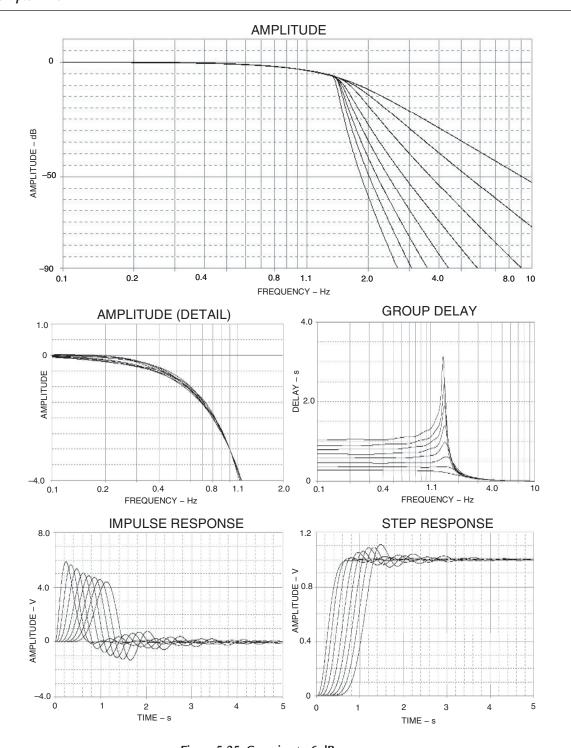

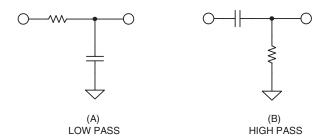

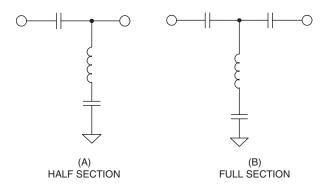

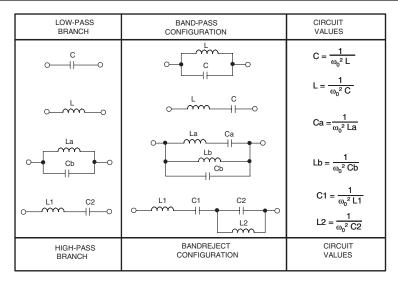

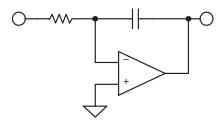

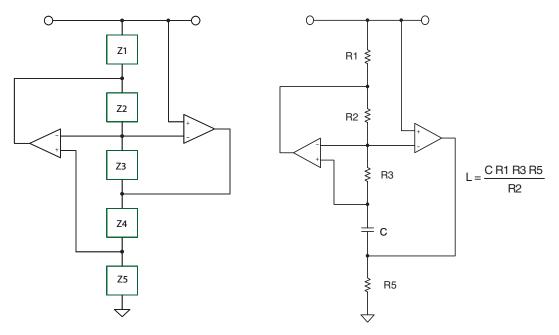

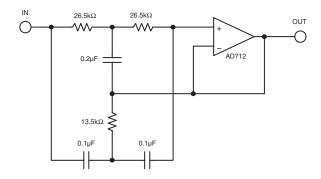

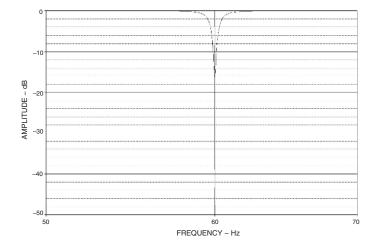

Chapter 5, *Analog Filters*, has eight sections authored by Hank Zumbahlen. This chapter could be considered a stand-alone treatise on how to implement modern analog filters. The eight sections, starting with an introduction, include transfer functions, time domain response, standard responses, frequency transformations, filter realizations, practical problems, and design examples. This chapter is more mathematical than any other within the book, with many response tables as design aids. One key highlight is the design example section, where an online filter-builder design tool is described in active filter implementation examples using Sallen-Key, multiple feedback, state variable, and frequency dependent negative resistance filter types. This chapter, another book-within-a-book, occupies about 114 pages.

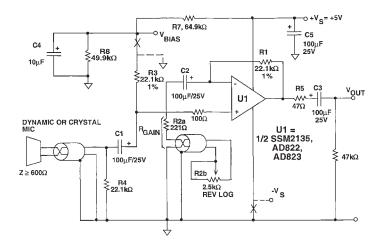

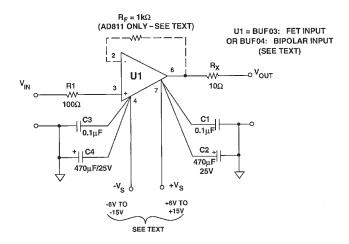

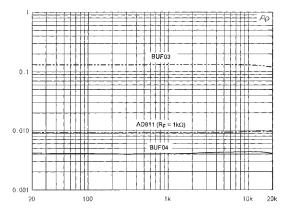

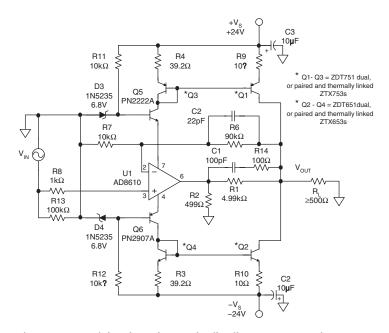

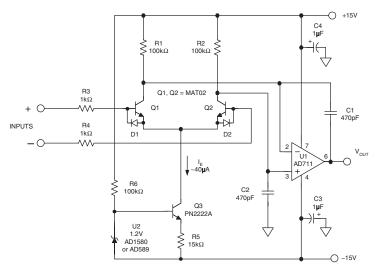

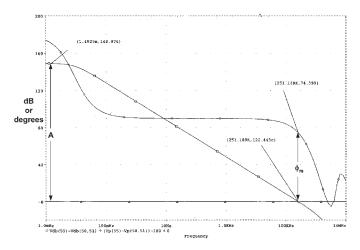

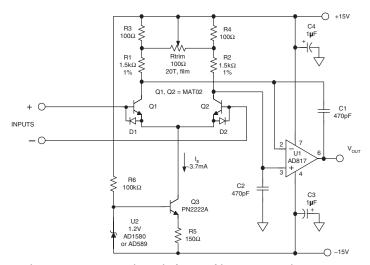

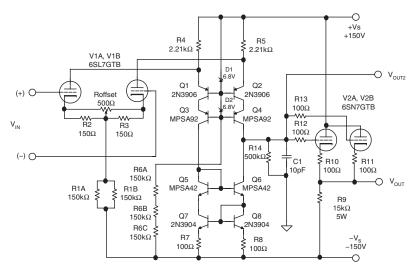

Chapter 6, *Signal Amplifiers*, has six sections authored by Walt Jung and Walt Kester. These sections are audio amplifiers, buffer amplifiers/driving capacitive loads, video amplifiers, communication amplifiers, amplifier ideas, and composite amplifiers. In the audio, video, and communications amplifier sections, various op amp circuit examples are shown, with emphasis in these sections on performance to high specifications— audio, video, or communications, as the case may be. The "amplifier ideas" section is a broad-range collection of various amplifier applications, selected for emphasis on creativity and innovation. The final section, on composite amplifiers, shows how additional discrete devices can be added to either the input or output of an op amp to enhance net performance. This book-within-a-book chapter occupies about 184 pages.

Chapter 7, *Hardware and Housekeeping Techniques*, has seven sections authored by Walt Kester, James Bryant, Walt Jung, Joe Buxton, and Wes Freeman. These sections are passive components, PCB design issues, op amp power supply systems, op amp input and output protection, thermal considerations, EMI/RFI considerations, and the final section, simulation, breadboarding and prototyping. All of these practical topics have a commonality that they are not completely covered (if at all) by the op amp data sheet. But, most importantly, they can be just as critical as the device specifications towards achieving the final results. This book-within-a-book chapter occupies about 158 pages.

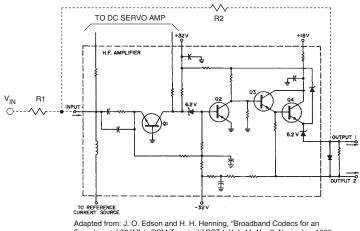

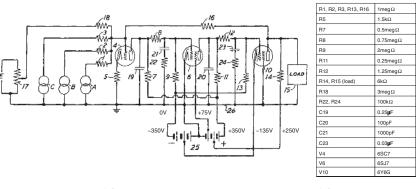

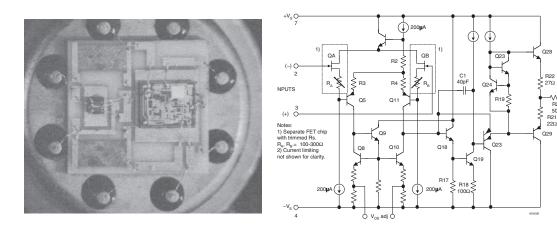

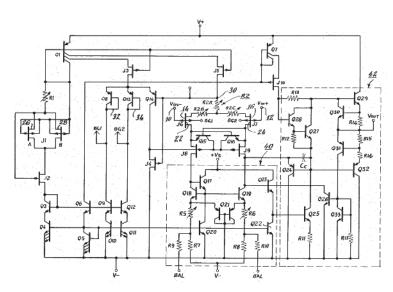

Chapter 8, the *History* chapter has four sections authored by Walt Jung. It provides a detailed account of not only the beginnings of operational amplifiers, but also their progress and the ultimate evolution into the IC form known today. This began with the underlying development of feedback amplifier principles, by Harold Black and others at Bell Telephone Laboratories. From the first practical analog computer feedback amplifier building blocks used during World War II, vacuum tube op amps later grew in sophistication, popularity

and diversity of use. The first solid-state op amps were "black-brick" plug in modules, which in turn were followed by hybrid IC forms, using chip semiconductors on ceramic substrates. The first monolithic IC op amp appeared in the early 1960s, and there have been continuous developments in circuitry, processes and packaging since then. This chapter occupies about 68 pages, and includes several hundred literature references.

The book is concluded with a thorough index with three pointer types: subject, ADI part number, and standard part numbers.

#### Acknowledgments

A book on a scale such as **Op Amp Applications Handbook** isn't possible without the work of many individuals. In the preparation phase many key contributions were made, and these are here acknowledged with sincere thanks. Of course, the first "Thank you" goes to ADI management, for project encouragement and support.

Hearty thanks goes next to Walt Kester of the ADI Central Applications Department, who freely offered his wisdom and counsel from many years of past ADI seminar publications. He also commented helpfully on the manuscript throughout. Special thanks go to Walt, as well as the many other named section authors who contributed material.

Thanks go also to the ADI Field Applications and Central Applications Engineers, who helped with comments and criticism. Ed Grokulsky, Bruce Hohman, Bob Marwin and Arnold Williams offered many helpful comments, and former ADI Applications Engineer Wes Freeman critiqued most of the manuscript, providing valuable feedback.

Special thanks goes to Dan Sheingold of ADI, who provided innumerable comments and critiques, and special insights from his many years of op amp experience dating from the vacuum tube era at George A. Philbrick Researches.

Thanks to Carolyn Hobson, who was instrumental in obtaining many of the historical references.

Thanks to Judith Douville for preparation of the index and helpful manuscript comments.

Walt Jung and Walt Kester together prepared slides for the book, and coordinated the stylistic design. Walt Jung did the original book page layout and typesetting.

#### Specific-to-Section Acknowledgments

Acknowledged here are focused comments from many individuals, specific to the section cited. All were very much appreciated.

#### Op Amp History; Introduction:

Particularly useful to this section of the project was reference information received from vacuum tube historian Gary Longrie. He provided information on early vacuum tube amplifiers, the feedback experiments of B. D. H. Tellegen at N. V. Philips, and made numerous improvement comments on the manuscript.

Mike Hummel provided the reference to Alan Blumlein's patent of a negative feedback amplifier.

Dan Sheingold provided constructive comments on the manuscript.

Bob Milne offered many comments towards improvement of the manuscript.

#### Op Amp History; Vacuum Tube Op Amps:

Particularly useful were numerous references on differential amplifiers, received from vacuum tube historian Gary Longrie. Gary also reviewed the manuscript and made numerous improvement comments. Without his enthusiastic inputs, the vacuum tube related sections of this narrative would be less complete.

Dan Sheingold supplied reference material, reviewed the manuscript, and made numerous constructive comments. Without his inputs, the vacuum tube op amp story would have less meaning.

Bel Losmandy provided many helpful manuscript inputs, including his example 1956 vacuum tube op amp design. He also reviewed the manuscript and made many helpful comments.

Paul de R. Leclercq and Morgan Jones supplied the reference to Blumlein's patent describing his use of a differential pair amplifier.

Bob Milne reviewed the manuscript and offered various improvement comments.

Steve Bench provided helpful comment on several points related to the manuscript.

#### Op Amp History; Solid-State Modular and Hybrid Op Amps:

Particularly useful was information from two GAP/R alumni, Dan Sheingold and Bob Pease. Both offered many details on the early days of working with George Philbrick, and Bob Pease furnished a previously unpublished circuit of the P65 amplifier.

Dick Burwen offered detailed information on some of his early ADI designs, and made helpful comments on the development of the narrative.

Steve Guinta and Charlie Scouten provided many of the early modular op amp schematics from the ADI Central Applications Department archival collection.

Lew Counts assisted with comments on the background of the high speed modular FET amplifier developments.

Walt Kester provided details on the HOS-050 amplifier and its development as a hybrid IC product at Computer Labs.

#### Op Amp History; IC Op Amps:

Many helpful comments on this section were received, and all are very much appreciated. In this regard, thanks go to Derek Bowers, JoAnn Close, Lew Counts, George Erdi, Bruce Hohman, Dave Kress, Bob Marwin, Bob Milne, Reza Moghimi, Steve Parks, Dan Sheingold, Scott Wurcer, and Jerry Zis

#### Op Amp Basics; Introduction:

Portions of this section were adapted from Ray Stata's "Operational Amplifiers - Part I," **Electromechanical Design**, September, 1965.

Bob Marwin, Dan Sheingold, Ray Stata, and Scott Wayne contributed helpful comments.

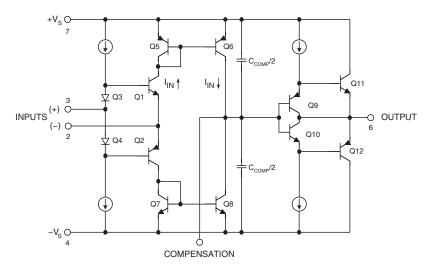

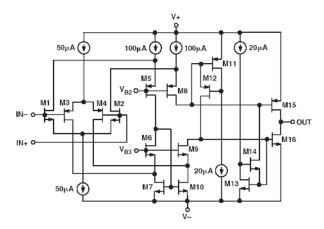

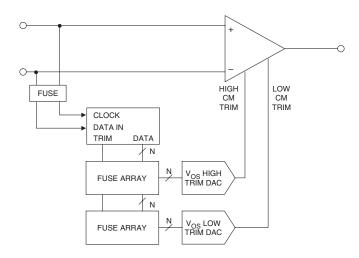

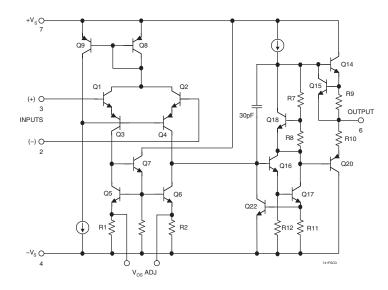

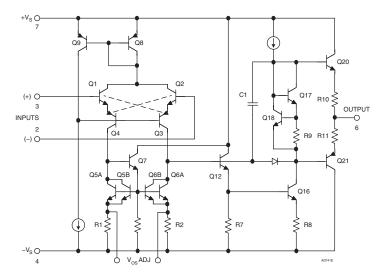

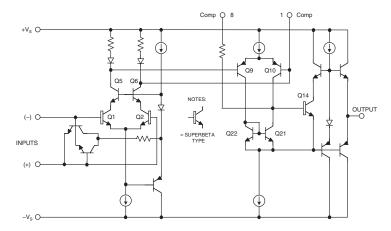

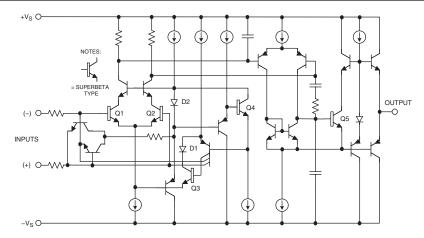

#### Op Amp Basics; Structures:

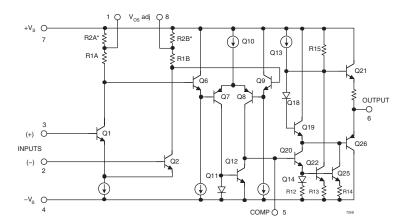

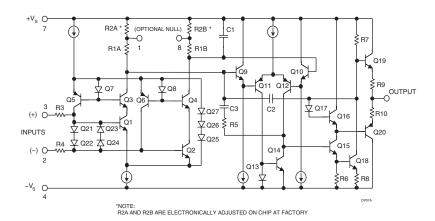

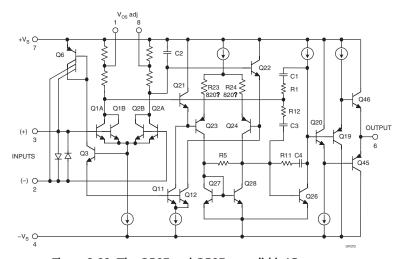

Helpful comments on various op amp schematics were received from ADI op amp designers Derek Bowers, Jim Butler, JoAnn Close, and Scott Wurcer.

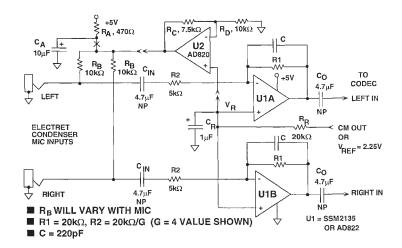

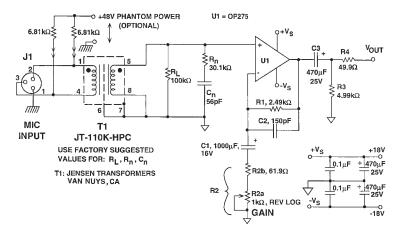

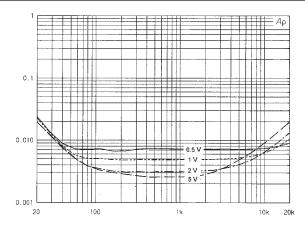

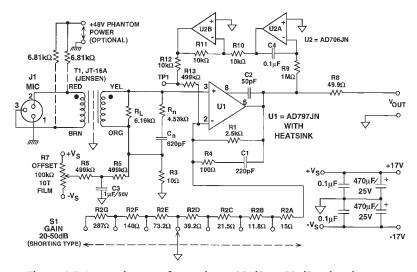

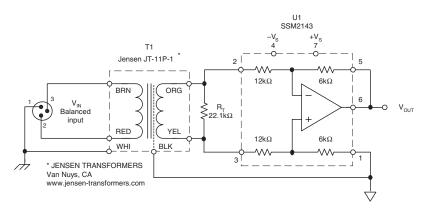

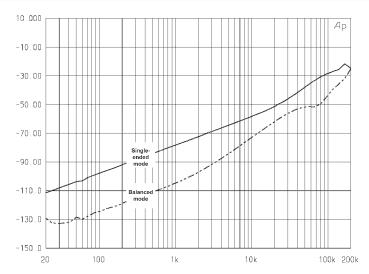

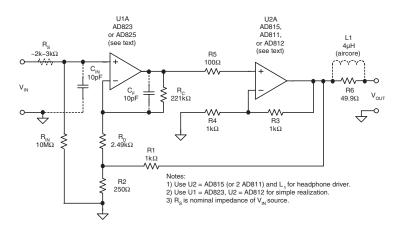

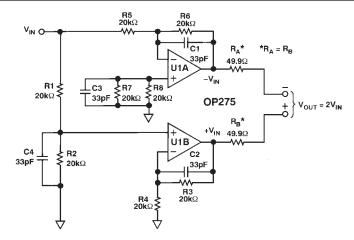

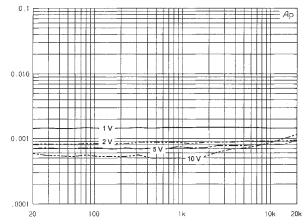

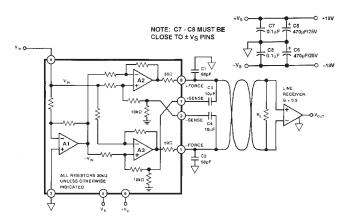

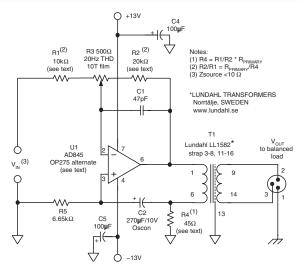

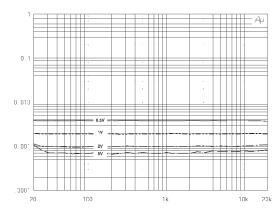

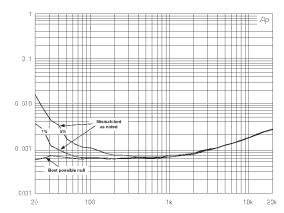

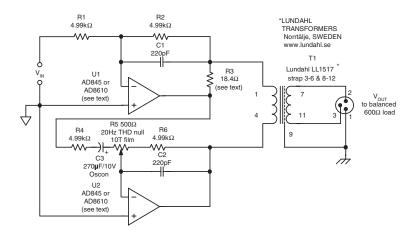

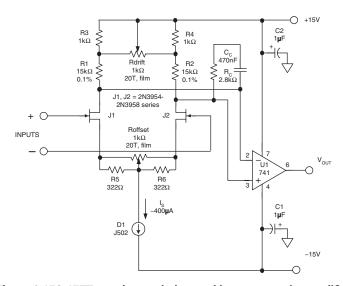

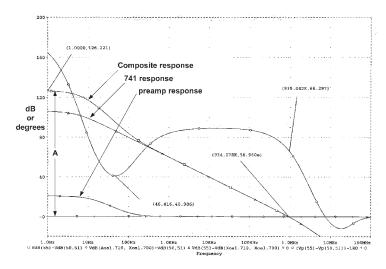

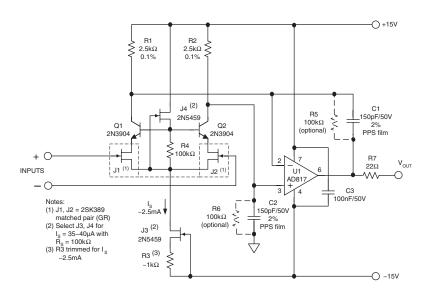

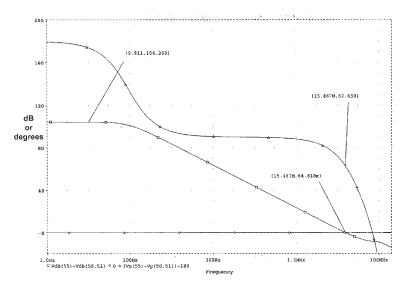

#### Signal Amplifiers; Audio Amplifiers:

Portions of this section were adapted from Walt Jung, "Audio Preamplifiers, Line Drivers, and Line Receivers," Chapter 8 of Walt Kester, **System Application Guide**, Analog Devices, Inc., 1993, ISBN 0-916550-13-3, pp. 8-1 to 8-100.

During the preparation of this material the author received helpful comments and other inputs from Per Lundahl of Lundahl Transformers, and from Arne Offenberg of Norway.

#### Signal Amplifiers; Amplifier Ideas:

Helpful comments were received from Victor Koren and Moshe Gerstenhaber.

#### Signal Amplifiers, Composite Amplifiers:

Helpful comments were received from Erno Borbely, Steve Bench, and Gary Longrie.

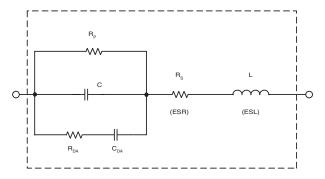

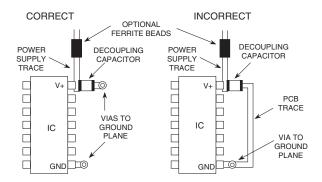

#### Hardware and Housekeeping Techniques; Passive Components and PCB Design Issues:

Portions of these sections were adapted from Doug Grant and Scott Wurcer, "Avoiding Passive Component Pitfalls," originally published in **Analog Dialogue 17-2**, 1983.

#### Hardware and Housekeeping Techniques; EMI/RFI Considerations:

Eric Bogatin made helpful comments on this section.

The above acknowledgments document helpful inputs received for the Analog Devices 2002 Amplifier Seminar edition of *Op Amp Applications*. In addition, Scott Wayne and Claire Shaw aided in preparation of the manuscript for this Newnes edition.

While reasonable efforts have been made to make this work error-free, some inaccuracies may have escaped detection. The editors accept responsibility for error correction within future editions, and will appreciate errata notification(s).

Walt Jung, Editor

Op Amp Applications Handbook

May 14, 2004

# Op Amp History Highlights

#### 1928

Harold S. Black applies for patent on his feedback amplifier invention.

#### 1930

Harry Nyquist applies for patent on his regenerative amplifier (patent issued in 1933).

#### 1937

U.S. Patent No. 2,102,671 issued to H.S. Black for "Wave Translation System."

B.D.H. Tellegen publishes a paper on feedback amplifiers, with attributions to H.S. Black and K. Posthumus.

Hendrick Bode files for an amplifier patent, issued in 1938.

#### 1941

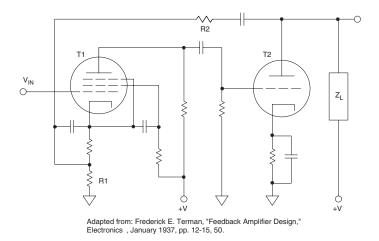

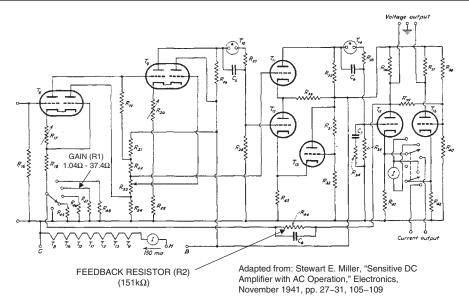

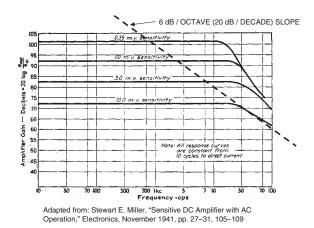

Stewart Miller publishes an article with techniques for high and stable gain with response to dc, introducing "cathode compensation."

Testing of prototype gun director system called the T10 using feedback amplifiers. This later leads to the M9, a weapon system instrumental in winning WWII.

Patent filed by Karl D. Swartzel Jr. of Bell Labs for a "Summing Amplifier," with a design that could well be the genesis of op amps. Patent not issued until 1946.

#### 1946

George Philbrick founds company, George A. Philbrick Researches, Inc. (GAP/R). His work was instrumental in op amp development.

#### 1947

Medal for Merit award given to Bell Labs's M9 designers Lovell, Parkinson, and Kuhn. Other contributors to this effort include Bode and Shannon.

Operational amplifiers first referred to by name in Ragazzini's key paper "Analysis of Problems in Dynamics by Electronic Circuits." It references the Bell Labs work on what became the M9 gun director, specifically referencing the op amp circuits used.

Bardeen, Brattain, and Shockley of Bell Labs discover the transistor effect.

#### 1948

George A. Philbrick publishes article describing a single-tube circuit that performs some op amp functions.

#### 1949

Edwin A. Goldberg invents chopper-stabilized vacuum tube op amp.

#### 1952

Granino and Theresa Korn publish textbook *Electronic Analog Computers*, which becomes a classic work on the uses and methodology of analog computing, with vacuum tube op amp circuits.

#### 1953

First commercially available vacuum tube op amp introduced by GAP/R.

#### 1954

Gordon Teal of Texas Instruments develops a silicon transistor.

#### 1956

GAP/R publishes manual for K2-W and related amplifiers, that becomes a seminal reference. Nobel Prize in Physics awarded to Bardeen, Brattain, and Shockley of Bell Labs for the transistor. Burr-Brown Research Corporation formed. It becomes an early modular solid-state op amp supplier.

#### 1958

Jack Kilby of Texas Instruments invents the integrated circuit (IC).

#### 1959

Jean A. Hoerni files for a patent on the planar process, a means of stabilizing and protecting semiconductors.

#### 1962

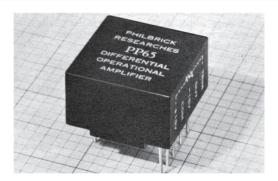

George Philbrick introduces the PP65, a square outline, 7-pin modular op amp which becomes a standard and allows the op amp to be treated as a *component*.

#### 1963

Bob Widlar of Fairchild designs the μA702, the first generally recognized monolithic IC op amp.

#### 1965

Fairchild introduces the milestone μA709 IC op amp, also designed by Bob Widlar.

Analog Devices, Inc. (ADI) is founded by Matt Lorber and Ray Stata. Op amps were their first product.

#### 1967

National Semiconductor Corp. (NSC) introduces the LM101 IC op amp, also designed by Bob Widlar, who moved to NSC from Fairchild. This device begins a second generation of IC op amps.

Analog Dialogue magazine is first published by ADI.

#### 1968

The  $\mu$ A741 op amp, designed by Dave Fullagar, is introduced by Fairchild and becomes the standard op amp.

#### 1969

Dan Sheingold takes over as editor of *Analog Dialogue* (and remains so today).

#### 1970

Model 45 high speed FET op amp introduced by ADI.

#### 1972

Russell and Frederiksen of National Semiconductor Corp. introduce an amplifier technique that leads to the LM324, the low cost, industry-standard general-purpose quad op amp.

#### 1973

Analog Devices introduces AD741, a high-precision 741-type op amp.

#### 1974

Ion implantation, a new fabrication technique for making FET devices, is described in a paper by Rod Russell and David Culner of National Semiconductor.

#### 1988

ADI introduces a high speed 36V CB process and a number of fast IC op amps. High performance op amps and op amps designed for various different categories continue to be announced throughout the 1980s and 1990s, and into the twenty-first century.

Chapter 8 provides a detailed narrative of op amp history.

# Op Amp Basics

- Section 1-1: Introduction

- Section 1-2: Op Amp Topologies

- Section 1-3: Op Amp Structures

- Section 1-4: Op Amp Specifications

- Section 1-5: Precision Op Amps

- Section 1-6: High Speed Op Amps

#### CHAPTER 1

# **Op Amp Basics**

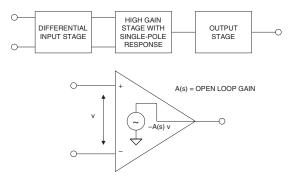

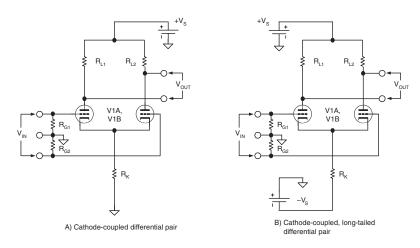

## James Bryant, Walt Jung, Walt Kester

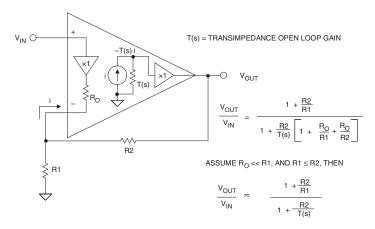

Within Chapter 1, discussions are focused on the basic aspects of op amps. After a brief introductory section, this begins with the fundamental *topology* differences between the two broadest classes of op amps, those using *voltage feedback* and *current feedback*. These two amplifier types are distinguished more by the nature of their internal circuit topologies than anything else. The voltage feedback op amp topology is the classic structure, having been used since the earliest vacuum tube based op amps of the 1940s and 1950s, through the first IC versions of the 1960s, and includes most op amp models produced today. The more recent IC variation of the current feedback amplifier has come into popularity in the mid-to-late 1980s, when higher speed IC op amps were developed. Factors distinguishing these two op amp types are discussed at some length.

Details of op amp input and output *structures* are also covered in this chapter, with emphasis on how such factors potentially impact application performance. In some senses, it is logical to categorize op amp types into performance and/or application classes, a process that works to some degree, but not altogether.

In practice, once past those obvious application distinctions such as "high speed" versus "precision," or "single" versus "dual supply," neat categorization breaks down. This is simply the way the analog world works. There is much crossover between various classes, i.e., a high speed op amp can be either single or dual-supply, or it may even fit as a precision type. A low power op amp may be precision, but it need not necessarily be single-supply, and so on. Other distinction categories could include the input stage type, such as FET input (further divided into JFET or MOS, which, in turn, are further divided into NFET or PFET and PMOS and NMOS, respectively), or bipolar (further divided into NPN or PNP). Then, all of these categories could be further described in terms of the type of input (or output) stage used.

So, it should be obvious that categories of op amps are like an infinite set of analog gray scales; *they don't always fit neatly into pigeonholes, and we shouldn't expect them to*. Nevertheless, it is still very useful to appreciate many of the aspects of op amp design that go into the various structures, as these differences directly influence the optimum op amp choice for an application. Thus structure differences are application drivers, since we choose an op amp to suit the nature of the application—for example, single-supply.

In this chapter various op amp performance *specifications* are also discussed, along with those specification differences that occur between the broad distinctions of voltage or current feedback topologies, as well as the more detailed context of individual structures. Obviously, op amp specifications are also application drivers; in fact, they are the most important since they will determine system performance. We choose the best op amp to fit the application, based on the required bias current, bandwidth, distortion, and so forth.

# Introduction

Walt Jung

As a precursor to more detailed sections following, this introductory chapter portion considers the most basic points of op amp operation. These initial discussions are oriented around the more fundamental levels of op amp applications. They include: *Ideal Op Amp Attributes*, *Standard Op Amp Feedback Hookups*, *The Non-Ideal Op Amp, Op Amp Common-Mode Dynamic Range(s)*, the various *Functionality Differences of Single and Dual-Supply Operation*, and the *Device Selection* process.

Before op amp applications can be developed, some requirements are in order. These include an understanding of how the fundamental op amp operating modes differ, and whether dual-supply or single-supply device functionality better suits the system under consideration. Given this, then device selection can begin and an application developed.

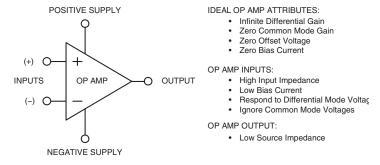

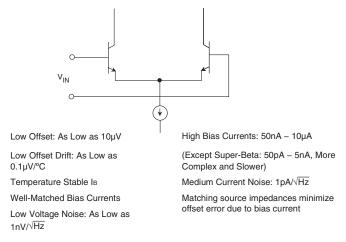

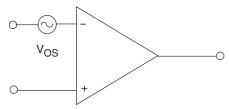

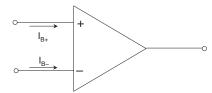

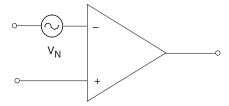

First, an *operational amplifier* (hereafter simply op amp) is a differential input, single-ended output amplifier, as shown symbolically in Figure 1-1. This device is an amplifier intended for use with *external feedback elements*, where these elements determine the resultant function, or *operation*. This gives rise to the name "operational amplifier," denoting an amplifier that, by virtue of different feedback hookups, can perform a variety of operations. At this point, note that there is no need for concern with any actual technology to implement the amplifier. Attention is focused more on the behavioral nature of this building block device.

Figure 1-1: The ideal op amp and its attributes

An op amp processes small, differential mode signals appearing between its two inputs, developing a single-ended output signal referred to a power supply common terminal. Summaries of the various ideal op amp attributes are given in Figure 1-1. While real op amps will depart from these ideal attributes, it is very helpful for first-level understanding of op amp behavior to consider these features. Further, although these initial discussions talk in idealistic terms, they are also flavored by pointed mention of typical "real world" specifications—for a beginning perspective.

<sup>&</sup>lt;sup>1</sup> The actual *naming* of the operational amplifier occurred in the classic Ragazinni, et al paper of 1947 (see Reference 1). However, analog computations using op amps as we know them today began with the work of the Clarence Lovell-led group at Bell Labs, around 1940 (acknowledged generally in the Ragazinni paper).

It is also worth noting that this op amp is shown with five terminals, a number that happens to be a minimum for real devices. While some single op amps may have more than five terminals (to support such functions as frequency compensation, for example), none will ever have fewer. By contrast, those elusive ideal op amps don't require power, and symbolically function with just four pins.<sup>2</sup>

#### Ideal Op Amp Attributes

An ideal op amp has infinite gain for *differential* input signals. In practice, real devices will have quite high gain (also called *open-loop gain*) but this gain won't necessarily be precisely known. In terms of specifications, gain is measured in terms of  $V_{OUT}/V_{IN}$ , and is given in V/V, the dimensionless numeric gain. More often, however, gain is expressed in decibel terms (dB), which is mathematically dB = 20 • log (numeric gain). For example, a numeric gain of 1 million (10<sup>6</sup> V/V) is equivalent to a 120 dB gain. Gains of 100 dB – 130 dB are common for precision op amps, while high speed devices may have gains in the 60 dB – 70 dB range.

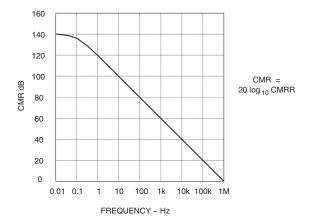

Also, an ideal op amp has zero gain for signals *common* to both inputs, that is, *common-mode* (CM) signals. Or, stated in terms of the rejection for these common-mode signals, an ideal op amp has infinite *CM rejection* (CMR). In practice, real op amps can have CMR specifications of up to 130 dB for precision devices, or as low as 60 dB–70 dB for some high speed devices.

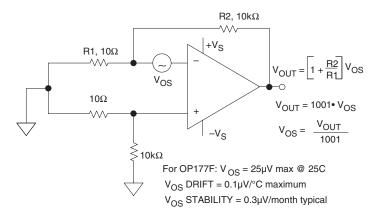

The ideal op amp also has zero *offset voltage* ( $V_{OS} = 0$ ), and draws zero *bias current* ( $I_B = 0$ ) at both inputs. Within real devices, actual offset voltages can be as low as 1  $\mu$ V or less, or as high as several mV. Bias currents can be as low as a few fA, or as high as several  $\mu$ A. This extremely wide range of specifications reflects the different input structures used within various devices, and is covered in more detail later in this chapter.

The attribute headings within Figure 1-1 for INPUTS and OUTPUT summarize the above concepts in more succinct terms. In practical terms, another important attribute is the concept of *low source impedance*, at the output. As will be seen later, low source impedance enables higher useful gain levels within circuits.

To summarize these idealized attributes for a signal processing amplifier, some of the traits might at first seem strange. However, it is critically important to reiterate that op amps simply are never intended for use without overall feedback. In fact, as noted, the connection of a suitable *external* feedback loop defines the *closed-loop* amplifier's gain and frequency response characteristics.

Note also that all real op amps have a positive and negative power supply terminal, but rarely (if ever) will they have a separate ground connection. In practice, the op amp output voltage becomes referred to a power supply common point. *Note: This key point is further clarified with the consideration of typically used op amp feedback networks.*

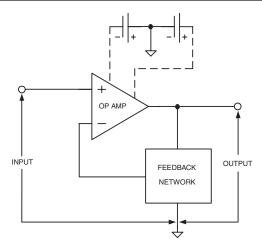

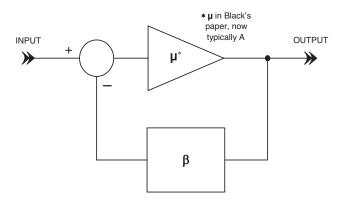

The basic op amp hookup of Figure 1-2 applies a signal to the (+) input, and a (generalized) network delivers a fraction of the output voltage to the (-) input terminal. This constitutes *feedback*, with the op amp operating in *closed-loop* fashion. The feedback network (shown here in general form) can be resistive or reactive, linear or nonlinear, or any combination of these. More detailed analysis will show that the circuit gain characteristic as a whole follows the inverse of the feedback network transfer function.

The concept of feedback is both an essential and salient point concerning op amp use. With feedback, the net closed-loop gain characteristics of a stage such as Figure 1-2 become primarily dependent upon a set of *external components* (usually passive). Thus behavior is less dependent upon the relatively unstable amplifier open-loop characteristics.

<sup>2</sup> Such an op amp generates its own power, has two input pins, an output pin, and an output common pin.

Figure 1-2: A generalized op amp circuit with feedback applied

Note that within Figure 1-2, the input signal is applied between the op amp (+) input and a *common* or *reference point*, as denoted by the ground symbol. It is important to note that this reference point is also common to the output and feedback network. By definition, the op amp stage's output signal appears between the output terminal/feedback network input, and this common ground. This single relevant fact answers the "Where is the op amp grounded?" question so often asked by those new to the craft. The answer is simply that it is grounded *indirectly*, by virtue of the commonality of its input, the feedback network, and the power supply, as is shown in Figure 1-2.

To emphasize how the input/output signals are referenced to the power supply, dual supply connections are shown dotted, with the  $\pm$  power supply midpoint common to the input/output signal ground. But do note, while all op amp application circuits may not show full details of the power supply connections, every *real* circuit will always use power supplies.

#### Standard Op Amp Feedback Hookups

Virtually all op amp feedback connections can be categorized into just a few basic types. These include the two most often used, *noninverting* and *inverting* voltage gain stages, plus a related *differential* gain stage. Having discussed above just the attributes of the ideal op amp, at this point it is possible to conceptually build basic gain stages. Using the concepts of infinite gain, zero input offset voltage, zero bias current, and so forth, standard op amp feedback hookups can be devised. For brevity, a full mathematical development of these concepts isn't included here (but this follows in a subsequent section). The end-of-section references also include such developments.

#### The Noninverting Op Amp Stage

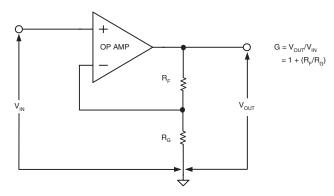

The op amp noninverting gain stage, also known as a *voltage follower with gain*, or simply *voltage follower*, is shown in Figure 1-3.

Figure 1-3: The noninverting op amp stage (voltage follower)

This op amp stage processes the input  $V_{IN}$  by a gain of G, so a generalized expression for gain is:

$$G = \frac{V_{OUT}}{V_{IN}}$$

Eq. 1-1

Feedback network resistances  $R_F$  and  $R_G$  set the stage gain of the follower. For an ideal op amp, the gain of this stage is:

$$G = \frac{R_F + R_G}{R_G}$$

Eq. 1-2

For clarity, these expressions are also included in the figure. Comparison of this figure and the more general Figure 1-2 shows  $R_F$  and  $R_G$  here as a simple feedback network, returning a fraction of  $V_{OUT}$  to the op amp (–) input. (Note that some texts may show the more general symbols  $Z_F$  and  $Z_G$  for these feedback components—both are correct, depending upon the specific circumstances.)

In fact, we can make some useful general points about the network  $R_F - R_G$ . We will define the transfer expression of the network as seen from the top of  $R_F$  to the output across  $R_G$  as  $\beta$ . Note that this usage is a general feedback network transfer term, *not* to be confused with bipolar transistor forward gain.  $\beta$  can be expressed mathematically as:

$$\beta = \frac{R_G}{R_F + R_G}$$

Eq. 1-3

So, the feedback network returns a fraction of  $V_{\text{OUT}}$  to the op amp (–) input. Considering the ideal principles of zero offset and infinite gain, this allows some deductions on gain to be made. The voltage at the (–) input is forced by the op amp's feedback action to be equal to that seen at the (+) input,  $V_{\text{IN}}$ . Given this relationship, it is relatively easy to work out the ideal gain of this stage, which in fact turns out to be simply the inverse of  $\beta$ . This is apparent from a comparison of Eqs. 1-2 and 1-3.

Thus an ideal noninverting op amp stage gain is simply equal to  $1/\beta$ , or:

$$G = \frac{1}{\beta}$$

Eq. 1-4

This noninverting gain configuration is one of the most useful of all op amp stages, for several reasons. Because  $V_{\text{IN}}$  sees the op amp's high impedance (+) input, it provides an ideal interface to the driving source. Gain can easily be adjusted over a wide range via  $R_F$  and  $R_G$ , with virtually no source interaction.

A key point is the interesting relationship concerning  $R_F$  and  $R_G$ . Note that to satisfy the conditions of Eq. 1-2, only their *ratio* is of concern. In practice this means that stable gain conditions can exist over a range of actual  $R_F - R_G$  values, so long as they provide the same ratio.

If  $R_F$  is taken to zero and  $R_G$  open, the stage gain becomes unity, and  $V_{OUT}$  is then exactly equal to  $V_{IN}$ . This special noninverting gain case is also called a *unity gain follower*, a stage commonly used for buffering a source.

Note that this op amp example shows only a simple resistive case of feedback. As mentioned, the feedback can also be reactive, i.e.,  $Z_{\text{F}}$  to include capacitors and/or inductors. In all cases, however, it must include a dc path, if we are to assume the op amp is being biased by the feedback (which is usually the case).

To summarize some key points on op amp feedback stages, we paraphrase from Reference 2 the following statements, which will always be found useful:

The summing point idiom is probably the most used phrase of the aspiring analog artificer, yet the least appreciated. In general, the inverting (-) input is called the summing point, while the noninverting (+) input is represented as the reference terminal. However, a vital concept is the fact that, within linear op amp applications, the inverting input (or summing point) assumes the same absolute potential as the noninverting input or reference (within the gain error of the amplifier). In short, the amplifier tries to servo its own summing point to the reference.

#### The Inverting Op Amp Stage

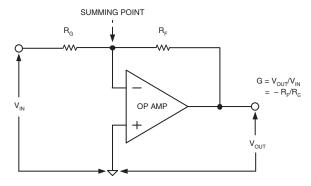

The op amp inverting gain stage, also known simply as the *inverter*, is shown in Figure 1-4. As can be noted by comparison of Figures 1-3 and 1-4, the inverter can be viewed as similar to a follower, but with a transposition of the input voltage  $V_{\rm IN}$ . In the inverter, the signal is applied to  $R_{\rm G}$  of the feedback network and the op amp (+) input is grounded.

Figure 1-4: The inverting op amp stage (inverter)

The feedback network resistances  $R_F$  and  $R_G$  set the stage gain of the inverter. For an ideal op amp, the gain of this stage is:

$$G = -\frac{R_F}{R_G}$$

Eq. 1-5

For clarity, these expressions are again included in the figure. Note that a major difference between this stage and the noninverting counterpart is the input-to-output sign reversal, denoted by the minus sign in Eq. 1-5. Like the follower stage, applying ideal op amp principles and some basic algebra can derive the gain expression of Eq. 1-5.

The inverting configuration is also one of the more useful op amp stages. Unlike a noninverting stage, however, the inverter presents a relatively low impedance input for  $V_{IN}$ , i.e., the value of  $R_G$ . This factor provides a finite load to the source. While the stage gain can in theory be adjusted over a wide range via  $R_F$  and  $R_G$ , there is a practical limitation imposed at high gain, when  $R_G$  becomes relatively low. If  $R_F$  is zero, the gain becomes zero.  $R_F$  can also be made variable, in which case the gain is linearly variable over the dynamic range of the element used for  $R_F$  As with the follower gain stage, the gain is ratio dependent, and is relatively insensitive to the exact  $R_F$  and  $R_G$  values.

The inverter's gain behavior, due to the principles of infinite op amp gain, zero input offset, and zero bias current, gives rise to an effective node of zero voltage at the (–) input. The input and feedback currents sum at this point, which logically results in the term *summing point*. It is also called a *virtual ground*, because of the fact it will be at the same potential as the grounded reference input.

Note that, technically speaking, *all* op amp feedback circuits have a summing point, whether they are inverters, followers, or a hybrid combination. The summing point is always the feedback junction at the (–) input node, as shown in Figure 1-4. However in follower type circuits this point isn't a virtual ground, since it follows the (+) input.

A special gain case for the inverter occurs when  $R_F = R_G$ , which is also called a *unity gain inverter*. This form of inverter is commonly used for generating complementary  $V_{OUT}$  signals, i.e.,  $V_{OUT} = -V_{IN}$ . In such cases it is usually desirable to match  $R_F$  to  $R_G$  accurately, which can readily be done by using a well-specified matched resistor pair.

A variation of the inverter is the *inverting summer*, a case similar to Figure 1-4, but with input resistors  $R_{G2}$ ,  $R_{G3}$ , etc (not shown). For a summer individual input resistors are connected to additional sources  $V_{IN2}$ ,  $V_{IN3}$ , and so forth, with their common node connected to the summing point. This configuration, called a *summing amplifier*, allows linear input current summation in  $R_{F}$ .  $^3V_{OUT}$  is proportional to an inverse sum of input currents.

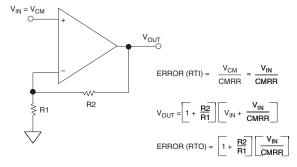

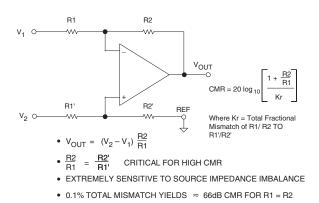

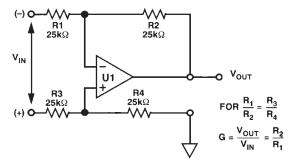

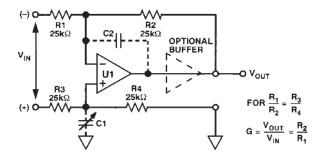

#### The Differential Op Amp Stage

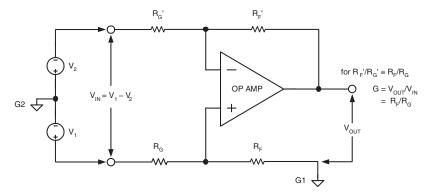

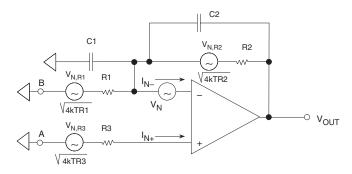

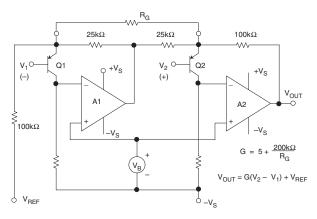

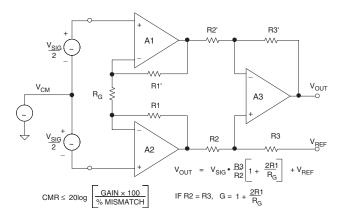

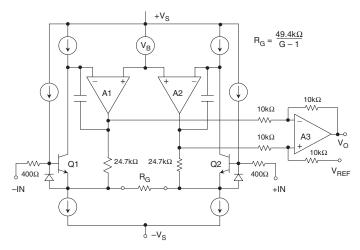

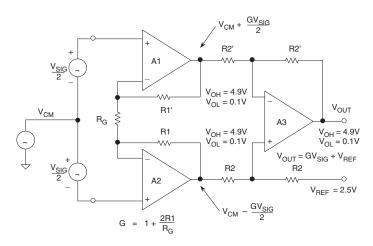

The op amp differential gain stage (also known as a *differential amplifier*, or *subtractor*) is shown in Figure 1-5. Paired input and feedback network resistances set the gain of this stage. These resistors,  $R_F - R_G$  and  $R_F' - R_G'$ , *must be matched as noted*, for proper operation. Calculation of individual gains for inputs  $V_1$  and  $V_2$  and their linear combination derives the stage gain.

<sup>&</sup>lt;sup>3</sup> The very first general-purpose op amp circuit is described by Karl Swartzel in Reference 3, and is titled "Summing Amplifier." This amplifier became a basic building block of the M9 gun director computer and fire control system used by Allied Forces in World War II. It also influenced many vacuum tube op amp designs that followed over the next two decades.

Figure 1-5: The differential amplifier stage (subtractor)

Note that the stage is intended to amplify the *difference* of voltages  $V_1$  and  $V_2$ , so the net input is  $V_{IN} = V_1 - V_2$ . The general gain expression is then:

$$G = \frac{V_{\text{OUT}}}{V_1 - V_2}$$

Eq. 1-6

For an ideal op amp and the resistor ratios matched as noted, the gain of this differential stage from  $V_{IN}$  to  $V_{OUT}$  is:

$$G = \frac{R_F}{R_G}$$

Eq. 1-7

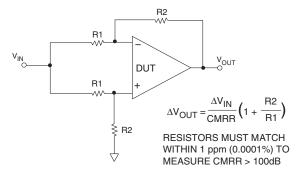

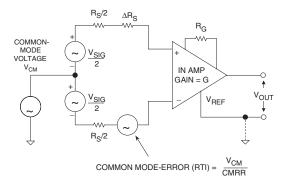

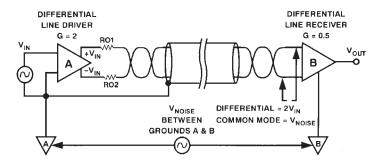

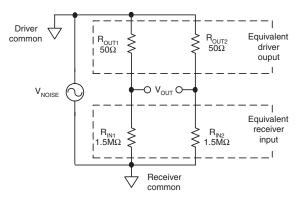

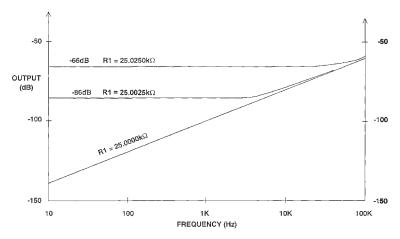

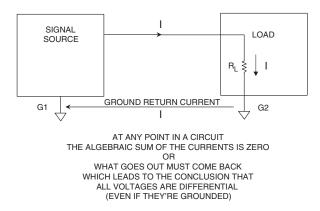

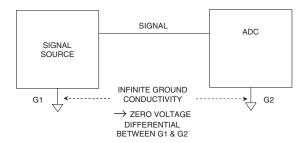

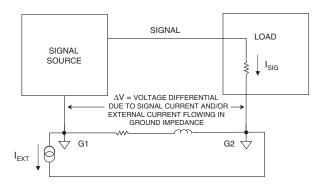

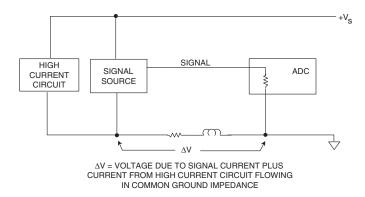

The great fundamental utility that an op amp stage such as this allows is the property of rejecting voltages *common* to  $V_1$ – $V_2$ , i.e., common-mode (CM) voltages. For example, if noise voltages appear between grounds G1 and G2, the noise will be suppressed by the common-mode rejection (CMR) of the differential amp. The CMR however is only as good as the matching of the resistor ratios allows, so in practical terms it implies precisely trimmed resistor ratios are necessary. Another disadvantage of this stage is that the resistor networks load the  $V_1$ – $V_2$  sources, potentially leading to additional errors.

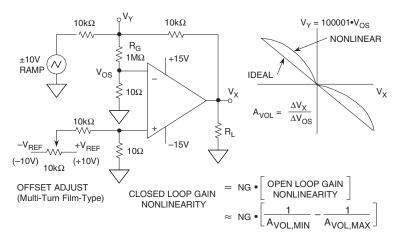

#### The Nonideal Op Amp—Static Errors Due to Finite Amplifier Gain

One of the most distinguishing features of op amps is their staggering magnitude of dc voltage gain. Even the least expensive devices have typical voltage gains of 100,000 (100 dB), while the highest performance precision bipolar and chopper stabilized units can have gains as high 10,000,000 (140 dB), or more. Negative feedback applied around this much voltage gain readily accomplishes the virtues of closed-loop performance, making the circuit dependent only on the feedback components.

As noted above in the discussion of ideal op amp attributes, the behavioral assumptions follow from the fact that negative feedback, coupled with high open-loop gain, constrains the amplifier input error voltage (and consequently the error current) to infinitesimal values. The higher this gain, the more valid these assumptions become.

In reality, however, op amps do have finite gain and errors exist in practical circuits. The op amp gain stage of Figure 1-6 will be used to illustrate how these errors impact performance. In this circuit the op amp is ideal except for the finite open-loop dc voltage gain, A, which is usually stated as  $A_{VOL}$ .

Figure 1-6: Nonideal op amp stage for gain error analysis

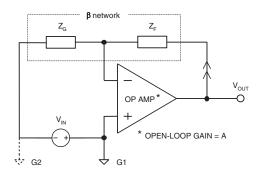

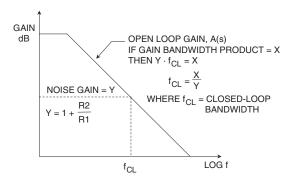

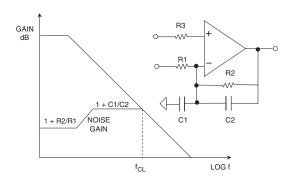

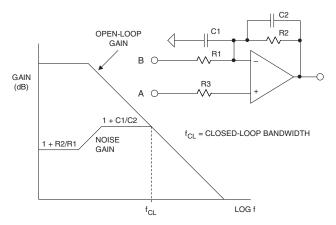

#### Noise Gain (NG)

The first aid to analyzing op amps circuits is to differentiate between *noise gain* and *signal gain*. We have already discussed the differences between noninverting and inverting stages as to their signal gains, which are summarized in Eqs. 1-2 and 1-4, respectively. But, as can be noticed from Figure 1-6, the difference between an inverting and noninverting stage can be as simple as where the reference ground is placed. For a ground at point G1, the stage is an inverter; conversely, if the ground is placed at point G2 (with no G1) the stage is noninverting.

Note, however, that in terms of the feedback path, there are no real differences. To make things more general, the resistive feedback components previously shown are replaced here with the more general symbols  $Z_F$  and  $Z_G$ , otherwise they function as before. The feedback attenuation,  $\beta$ , is the same for both the inverting and noninverting stages:

$$\beta = \frac{Z_G}{Z_G + Z_F}$$

Eq. 1-8

Noise gain can now be simply defined as: The inverse of the net feedback attenuation from the amplifier output to the feedback input. In other words, the inverse of the  $\beta$  network transfer function. This can ultimately be extended to include frequency dependence (covered later in this chapter). Noise gain can be abbreviated as NG.

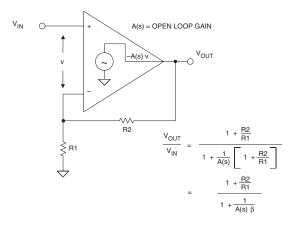

As noted, the inverse of  $\beta$  is the ideal noninverting op amp stage gain. Including the effects of finite op amp gain, a modified gain expression for the noninverting stage is:

$$G_{CL} = \frac{1}{\beta} \times \left[ \frac{1}{1 + \frac{1}{A_{VOL}\beta}} \right]$$

Eq. 1-9

where  $G_{CL}$  is the finite-gain stage's closed-loop gain, and  $A_{VOL}$  is the op amp open-loop voltage gain for loaded conditions.

It is important to note that this expression is identical to the ideal gain expression of Eq. 1-4, with the addition of the bracketed multiplier on the right side. Note also that this right-most term becomes closer and closer to unity, as  $A_{VOL}$  approaches infinity. Accordingly, it is known in some textbooks as the *error multiplier* term, when the expression is shown in this form.<sup>4</sup>

It may seem logical here to develop another finite gain error expression for an inverting amplifier, but in actuality there is no need. Both inverting and noninverting gain stages have a common feedback basis, which is the noise gain. So Eq. 1-9 will suffice for gain error analysis for both stages. Simply use the  $\beta$  factor as it applies to the specific case.

It is useful to note some assumptions associated with the rightmost error multiplier term of Eq. 1-9. For  $A_{VOL}\beta >> 1$ , one assumption is:

$$\frac{1}{1 + \frac{1}{A_{\text{VOL}}\beta}} \approx 1 - \frac{1}{A_{\text{VOL}}\beta}$$

Eq. 1-10

This in turn leads to an estimation of the percentage error,  $\varepsilon$ , due to finite gain  $A_{VOI}$ :

$$\varepsilon(\%) \approx \frac{100}{A_{\text{vol}} \beta}$$

Eq. 1-11

#### Gain Stability

The closed-loop gain error predicted by these equations isn't in itself tremendously important, since the ratio  $Z_F/Z_G$  could always be adjusted to compensate for this error.

But note however that closed-loop gain *stability* is a very important consideration in most applications. Closed-loop gain instability is produced primarily by variations in open-loop gain due to changes in temperature, loading, and so forth.

$$\frac{\Delta G_{CL}}{G_{Cl}} \approx \frac{\Delta A_{VOL}}{A_{VOL}} \times \frac{1}{A_{VOL}} \beta$$

Eq. 1-12

From Eq. 1-12, any variation in open-loop gain  $(\Delta A_{VOL})$  is reduced by the factor  $A_{VOL}\beta$ , insofar as the effect on closed-loop gain. This improvement in closed-loop gain stability is one of the important benefits of negative feedback.

#### **Loop Gain**

The product  $A_{VOL}\beta$ , which occurs in the above equations, is called *loop gain*, a well-known term in feedback theory. The improvement in closed-loop performance due to negative feedback is, in nearly every case, proportional to loop gain.

The term "loop gain" comes from the method of measurement. This is done by breaking the closed feedback loop at the op amp output, and measuring the total gain around the loop. In Figure 1-6 for example, this could be done between the amplifier output and the feedback path (see arrows). To a first

<sup>&</sup>lt;sup>4</sup> Some early discussions of this finite gain error appear in References 4 and 5. Terman uses the open-loop gain symbol of A, as we do today. West uses Harold Black's original notation of μ for open-loop gain. The form of Eq. 1-9 is identical to Terman's (or to West's, substituting μ for A).

approximation, closed-loop output impedance, linearity, and gain stability are all reduced by  $A_{\text{VOL}}\beta$  with the use of negative feedback.

Another useful approximation is developed as follows. A rearrangement of Eq. 1-9 is:

$$\frac{A_{\text{VOL}}}{G_{\text{CL}}} = 1 + A_{\text{VOL}}\beta$$

Eq. 1-13

So, for high values of  $A_{VOL}\beta$ ,

$$\frac{A_{\text{VOL}}}{G_{\text{CL}}} \approx A_{\text{VOL}} \beta$$

Eq. 1-14

Consequently, in a given feedback circuit the loop gain,  $A_{VOL}\beta$ , is approximately the numeric ratio (or difference, in dB) of the amplifier open-loop gain to the circuit closed-loop gain.

This loop gain discussion emphasizes that, indeed, loop gain is a very significant factor in predicting the performance of closed-loop operational amplifier circuits. The open-loop gain required to obtain an adequate amount of loop gain will, of course, depend on the desired closed-loop gain.

For example, using Eq. 1-14, an amplifier with  $A_{VOL} = 20,000$  will have an  $A_{VOL}\beta \approx 2000$  for a closed-loop gain of 10, but the loop gain will be only 20 for a closed-loop gain of 1000. The first situation implies an amplifier-related gain error on the order of  $\approx 0.05\%$ , while the second would result in about 5% error. Obviously, the higher the required gain, the greater will be the required open-loop gain to support an  $A_{VOL}\beta$  for a given accuracy.

#### Frequency Dependence of Loop Gain

Thus far, it has been assumed that amplifier open-loop gain is independent of frequency. Unfortunately, this isn't the case. Leaving the discussion of the effect of open-loop response on bandwidth and dynamic errors until later, let us now investigate the general effect of frequency response on loop gain and static errors.

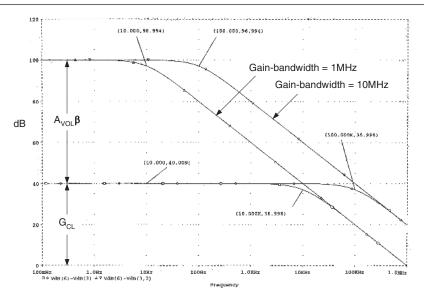

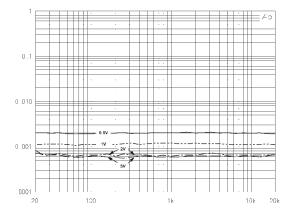

The open-loop frequency response for a typical operational amplifier with superimposed closed-loop amplifier response for a gain of 100 (40 dB), illustrates graphically these results in Figure 1-7. In these Bode plots, subtraction on a logarithmic scale is equivalent to normal division of numeric data.<sup>5</sup> Today, op amp open-loop gain and loop gain parameters are typically given in dB terms, thus this display method is convenient.

A few key points evolve from this graphic figure, which is a simulation involving two hypothetical op amps, both with a dc/low frequency gain of 100 dB (100 kV/V). The first has a gain-bandwidth of 1 MHz, while the gain-bandwidth of the second is 10 MHz.

- The open-loop gain A<sub>VOL</sub> for the two op amps is noted by the two curves marked 1 MHz and 10 MHz, respectively. Note that each has a –3 dB corner frequency associated with it, above which the open-loop gain falls at 6 dB/octave. These corner frequencies are marked at 10 Hz and 100 Hz, respectively, for the two op amps.

- At any frequency on the open-loop gain curve, the numeric product of gain A<sub>VOL</sub> and frequency, f, is a constant (10,000 V/V at 100 Hz equates to 1 MHz). This, by definition, is characteristic of a constant gain-bandwidth product amplifier. All *voltage feedback* op amps behave in this manner.

The log-log displays of amplifier gain (and phase) versus frequency are called *Bode* plots. This graphic technique for display of feedback amplifier characteristics, plus definitions for feedback amplifier stability were pioneered by Hendrick W. Bode of Bell Labs (see Reference 6).

Figure 1-7: Op amp closed-loop gain and loop gain interactions with typical open-loop responses

- $A_{VOL}\beta$  in dB is the difference between open-loop gain and closed-loop gain, as plotted on log-log scales. At the lower frequency point marked,  $A_{VOL}\beta$  is thus 60 dB.

- $A_{VOL}\beta$  decreases with increasing frequency, due to the decrease of  $A_{VOL}$  above the open-loop corner frequency. At 100 Hz for example, the 1 MHz gain-bandwidth amplifier shows an  $A_{VOL}\beta$  of only 80 db 40 db = 40 dB.

- $A_{VOL}\beta$  also decreases for higher values of closed-loop gain. Other, higher closed-loop gain examples (not shown) would decrease  $A_{VOL}\beta$  to less than 60 dB at low frequencies.

- $G_{CL}$  depends primarily on the ratio of the feedback components,  $Z_F$  and  $Z_G$ , and is relatively independent of  $A_{VOL}$  (apart from the errors discussed above, which are inversely proportional to  $A_{VOL}\beta$ ). In this example  $1/\beta$  is 100, or 40 dB, and is so marked at 10 Hz. Note that  $G_{CL}$  is flat with increasing frequency, up until that frequency where  $G_{CL}$  intersects the open-loop gain curve, and  $A_{VOL}\beta$  drops to zero.

- At this point where the closed-loop and open-loop curves intersect, the loop gain is by definition zero, which implies that beyond this point there is no negative feedback. Consequently, closed-loop gain is equal to open-loop gain for further increases in frequency.

- Note that the 10 MHz gain-bandwidth op amp allows a 10× increase in closed-loop bandwidth, as can be noted from the -3 dB frequencies; that is 100 kHz versus 10 kHz for the 10 MHz versus the 1 MHz gain-bandwidth op amp.

Figure 1-7 illustrates that the high open-loop gain figures typically quoted for op amps can be somewhat misleading. As noted, beyond a few Hz, the open-loop gain falls at 6 dB/octave. Consequently, closed-loop gain stability, output impedance, linearity and other parameters dependent upon loop gain are degraded at higher frequencies. One of the reasons for having dc gain as high as 100 dB and bandwidth as wide as several MHz, is to obtain adequate loop gain at frequencies even as low as 100 Hz.

A direct approach to improving loop gain at high frequencies, other than by increasing open-loop gain, is to increase the amplifier open-loop bandwidth. Figure 1-7 shows this in terms of two simple examples. It should be borne in mind however that op amp gain-bandwidths available today extend to the hundreds of MHz, allowing video and high-speed communications circuits to fully exploit the virtues of feedback.

#### Op Amp Common-Mode Dynamic Range(s)

As a point of departure from the idealized circuits above, some practical basic points are now considered. Among the most evident of these is the allowable input and output dynamic ranges afforded in a real op amp. This obviously varies with not only the specific device, but also the supply voltage. While we can always optimize this performance point with device selection, more fundamental considerations come first.

Any real op amp will have a finite voltage range of operation, at both input and output. In modern system designs, supply voltages are dropping rapidly, and 3 V - 5 V total supply voltages are now common. This is a far cry from supply systems of the past, which were typically  $\pm 15 \text{ V}$  (30 V total). Obviously, if designs are to accommodate a 3 V - 5 V supply, careful consideration must be given to maximizing dynamic range, by choosing a correct device. Choosing a device will be in terms of exact specifications, but first and foremost it should be in terms of the basic topologies used within it.

#### **Output Dynamic Range**

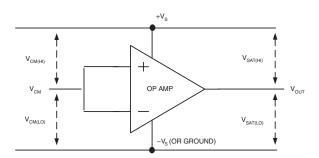

Figure 1-8 is a general illustration of the limitations imposed by input and output dynamic ranges of an op amp, related to both supply rails. Any op amp will always be powered by two supply potentials, indicated by the positive rail,  $+V_s$ , and the negative rail,  $-V_s$ . We will define the op amp's input and output CM range in terms of how closely it can approach these two rail voltage limits.

Figure 1-8: Op amp input and output common-mode ranges

At the output,  $V_{OUT}$  has two rail-imposed limits, one high or close to  $+V_S$ , and one low, or close to  $-V_S$ . Going high, it can range from an upper saturation limit of  $+V_S - V_{SAT(HI)}$  as a positive maximum. For example if  $+V_S$  is 5 V, and  $V_{SAT(HI)}$  is 100 mV, the upper  $V_{OUT}$  limit or positive maximum is 4.9 V. Similarly, going low it can range from a lower saturation limit of  $-V_S + V_{SAT(LO)}$ . So, if  $-V_S$  is ground (0 V) and  $V_{SAT(HI)}$  is 50 mV, the lower limit of  $V_{OUT}$  is simply 50 mV.

Obviously, the internal design of a given op amp will impact this output CM dynamic range, since, when so necessary, the device itself must be designed to minimize both  $V_{\text{SAT(HI)}}$  and  $V_{\text{SAT(LO)}}$ , to maximize the output dynamic range. Certain types of op amp structures are so designed, and these are generally associated with designs expressly for *single-supply* systems. This is covered in detail later within the chapter.

#### Input Dynamic Range

At the input, the CM range useful for  $V_{IN}$  also has two rail-imposed limits, one high or close to  $+V_s$ , and one low, or close to  $-V_s$ . Going high, it can range from an upper CM limit of  $+V_s - V_{CM(HI)}$  as a positive maximum. For example, again using the  $+V_s = 5$  V example case, if  $V_{CM(HI)}$  is 1 V, the upper  $V_{IN}$  limit or positive CM maximum is  $+V_s - V_{CM(HI)}$ , or 4 V.

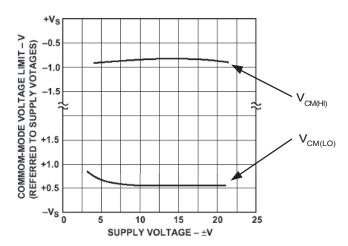

Figure 1-9 illustrates by way of a hypothetical op amp's data how  $V_{\text{CM(HI)}}$  could be specified, as shown in the upper curve. This particular op amp would operate for  $V_{\text{CM}}$  inputs *lower* than the curve shown.

Figure 1-9: A graphical display of op amp input common mode range

In practice the input CM range of real op amps is typically specified as a *range of voltages*, not necessarily referenced to  $+V_S$  or  $-V_S$ . For example, a typical  $\pm 15$  V operated dual supply op amp would be specified for an operating CM range of  $\pm 13$  V. Going low, there will also be a lower CM limit. This can be generally expressed as  $-V_S + V_{CM(LO)}$ , which would appear in a graph such as Figure 1-9 as the lower curve, for  $V_{CM(LO)}$ . If this were again a  $\pm 15$  V part, this could represent typical performance.

To use a single-supply example, for the  $-V_s = 0$  V case, if  $V_{CM(LO)}$  is 100 mV, the lower CM limit will be 0 V + 0.1 V, or simply 0.1 V. Although this example illustrates a lower CM range within 100 mV of  $-V_s$ , it is actually much more typical to see single-supply devices with lower or upper CM ranges, which *include* the supply rail.

In other words,  $V_{\text{CM(LO)}}$  or  $V_{\text{CM(HI)}}$  is 0 V. There are also single-supply devices with CM ranges that include *both* rails. More often than not, however, single-supply devices will not offer graphical data such as Figure 1-9 for CM limits, but will simply cover performance with a tabular range of specified voltage.

#### Functionality Differences of Dual-Supply and Single-Supply Devices

There are two major classes of op amps, the choice of which determines how well the selected part will function in a given system. Traditionally, many op amps have been designed to operate on a dual power supply system, which has typically been  $\pm 15$  V. This custom has been prevalent since the earliest IC op amps days, dating back to the mid-sixties. Such devices can accommodate input/output ranges of  $\pm 10$  V (or slightly more), but when operated on supplies of appreciably lower voltage, for example  $\pm 5$  V or less, they suffer either loss of performance, or simply don't operate at all. This type of device is referenced here as a *dual-supply* op amp design. This moniker indicates that it performs optimally on dual voltage systems only, typically  $\pm 15$  V. It may or may not also work at appreciably lower voltages.

Figure 1-10 illustrates in a broad overview the relative functional performance differences that distinguish the dual-supply versus single-supply op amp classes. This table is arranged to illustrate various general performance parameters, with an emphasis on the contrast between single-and dual-supply devices. Which particular performance area is more critical will determine which type of device will be the better system choice.

| DITAL CLIDDLY             | SINGLE SUPPLY                                                               |

|---------------------------|-----------------------------------------------------------------------------|

| DUAL SUFFLI               | SINGLE SUFFLI                                                               |

| Best >10V,                | Best <10V,                                                                  |

| Limited <10V              | Limited >10V                                                                |

| - Limited                 | + Greatest                                                                  |

|                           |                                                                             |

| <ul><li>Limited</li></ul> | + Greatest                                                                  |

|                           |                                                                             |

| + Greatest                | <ul><li>Least</li></ul>                                                     |

|                           |                                                                             |

|                           |                                                                             |

| + Greater                 | – Less                                                                      |

| + Greatest                | <ul><li>Less (growing)</li></ul>                                            |

| + Greatest                | <ul><li>Least</li></ul>                                                     |

|                           |                                                                             |

| + Greater                 | <ul><li>Less (growing)</li></ul>                                            |

|                           |                                                                             |

|                           | Limited <10V - Limited - Limited + Greatest + Greater + Greatest + Greatest |

Figure 1-10: Comparison of relative functional performance differences between single and dual-supply op amps

More recently, with increasing design attention to lower overall system power and the use of single rail power, the single-supply op amp has come into vogue. This has not been without good reason, as the virtues of using single supply rails can be quite compelling. A review of Figure 1-10 illustrates key points of the dual versus single supply op amp question.

In terms of *supply voltage limitations*, there is a crossover region in terms of overall utility, which occurs around 10 V of total supply voltage.

For example, single-supply devices tend to excel in terms of their *input and output voltage dynamic ranges*. Note that in Figure 1-10 a maximum range is stated as a percentage of available supply. Single-supply parts operate better in this regard, because they are internally designed to maximize these respective ranges. For example, it is not unusual for a device operating from 5 V to swing 4.8 V at the output, and so on.

But, rather interestingly, such devices are also usually restricted to lower supply ranges (only), so their upper dynamic range in absolute terms is actually more limited. For example, a traditional  $\pm 15~V$

dual-supply device can typically swing 20 V p-p, or more than four times that of a 5 V single-supply part. If the *total dynamic range* is considered (assuming an identical input noise), the dual-supply operated part will have four times (or 12 dB) greater dynamic range than that of the 5 V operated part. Or, stated in another way, the input errors of a real part such as noise, drift, and so forth, become four times more critical (relatively speaking), when the output dynamic range is reduced by a factor of 4. Note that these comparisons do not involve any actual device specifications, *they are simply system-based observations*. Device specifications are covered later in this chapter.

In terms of total *voltage and current output*, dual-supply parts tend to offer more in absolute terms, since single-supply parts are usually designed not just for low operating voltage ranges, but also for more modest current outputs.

In terms of *precision*, the dual-supply op amp has long been favored by designers for highest overall precision. However, this status quo is now beginning to be challenged, by such single-supply parts as the truly excellent chopper-stabilized op amps. With more and more new op amps being designed for single-supply use, high precision is likely to become an ever-increasing strength of this category.

*Load immunity* is often an application problem with single-supply parts, as many of them use common-emitter or common-source output stages, to maximize signal swing. Such stages are typically much more load sensitive than the classic common-collector stages generally used in dual-supply op amps.

There is now a greater *variety* of dual-supply op amps available. However, this is at least in part due to the ~30-year head start they have been enjoying. Currently, new op amp designs are increasingly oriented around one or more aspects of single-supply compatibility, with strong trends toward lower supply voltages, smaller packages, and so forth.

#### **Device Selection Drivers**

As the op amp design process is begun, it is useful to keep in mind the fact that there are several selection *drivers*, which can dictate priorities. This is illustrated by Figure 1-11.

| FUNCTION      | PERFORM     | PACKAGE   | MARKET       |

|---------------|-------------|-----------|--------------|

|               |             |           |              |

| Single, Dual, | Precision   | Туре      | Cost         |

| Quad          |             |           |              |

| Single Or     | Speed       | Size      | Availability |

| Dual Supply   |             |           |              |

| Supply        | Distortion, | Footprint |              |

| Voltage       | Noise       |           |              |

|               | Low Bias    |           |              |

|               | Current     |           |              |

|               | Power       |           |              |

Figure 1-11: Some op amp selection drivers

Actually, any *single* heading along the top of this chart can, in fact, be the dominant selection driver and take precedence over all of the others. In the early days of op amp design, when such things as supply range, package type, and so forth, were fairly narrow in spread, performance was usually the major driver. Of course, it is still very much so and will always be. But, today's systems are much more compact and lower in power, so things like package type, size, supply range, and multiple devices can often be major drivers of selection. As one example, if the only available supply voltage is 3 V, look at 3 V compatible devices first, and then fill other performance parameters as you can.

As another example, one coming from another perspective, sometimes all-out performance can drive everything else. An ultralow, non-negotiable input current requirement can drive not only the type of amplifier, but also its package (a FET input device in a glass-sealed hermetic package may be optimum). Then, everything else follows from there. Similarly, high power output may demand a package capable of several watts dissipation; in which case, find the power handling device and package first, and then proceed accordingly.

At this point, the concept of these "selection drivers" is still quite general. The following sections of the chapter introduce device types, which supplement this with further details of a realistic selection process.

#### Classic Cameo

# Ray Stata Publications Establish ADI Applications Work